已解决

ZYNQ_project:led

来自网友在路上 163863提问 提问时间:2023-11-10 00:23:35阅读次数: 63

最佳答案 问答题库638位专家为你答疑解惑

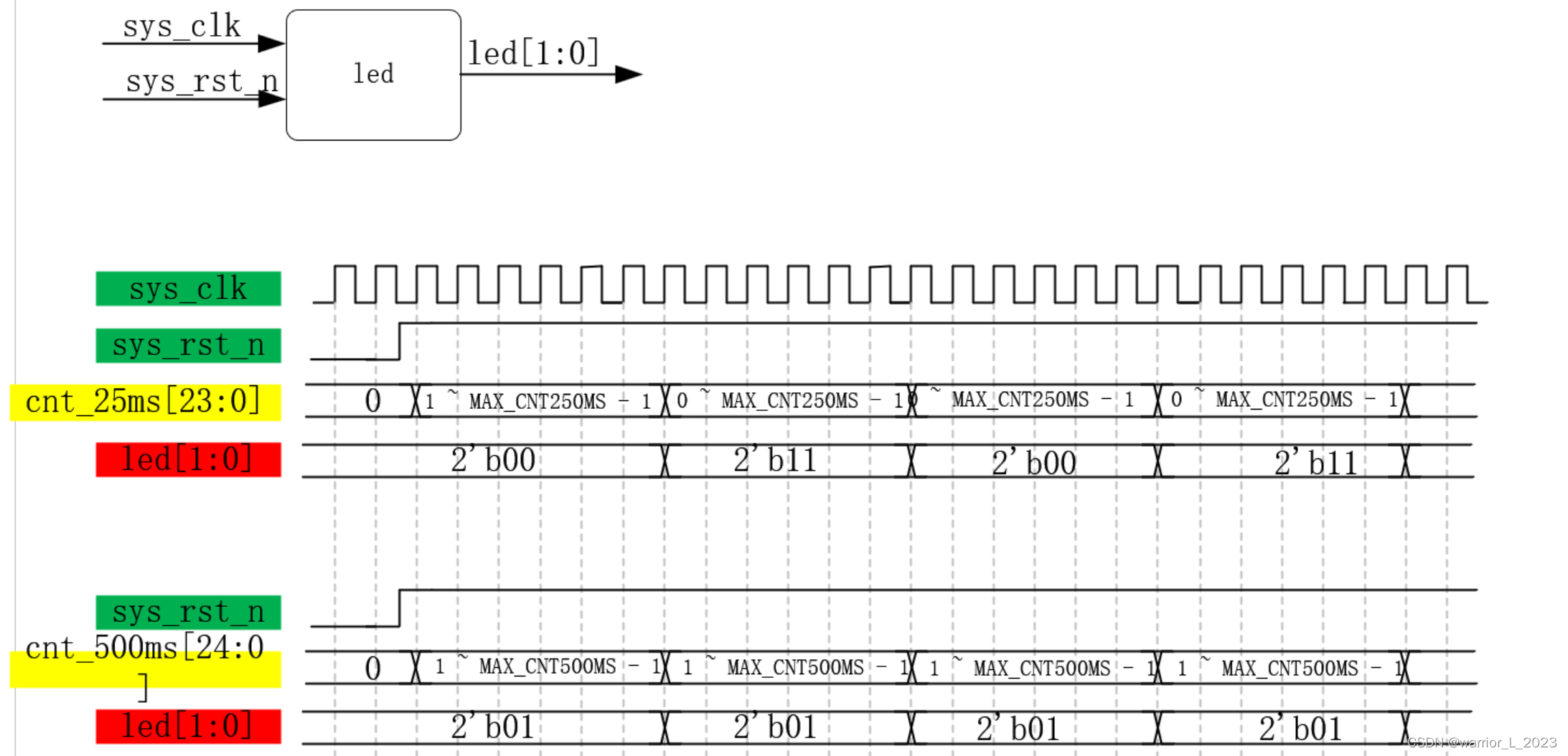

本次实验完成:led流水间隔0.5s

闪烁间隔0.25s。

名词解释:

analysis分析:对源文件进行全面的语法检查。

synthesis综合:综合的过程是由 FPGA 综合工具箱 HDL 原理图或其他形式源文件进行分析,进而推演出由 FPGA 芯片中底层基本单元表示的电路网表的过程。通俗的讲就是将自己的设计映射到 FPGA 中。

Implementation设计实现:加入一些约束文件。然后可以进行后仿真。

bitstream生成bit流文件:下载进开发板。

时序图:

代码:

分为流水与闪烁。

// led闪烁实验,间隔0.25s

module led(input wire sys_clk ,input wire sys_rst_n ,output reg [1:0] led_out

);parameter MAX_CNT25MS = 1_250_0000 ;reg [23:0] cnt_25ms ;wire cnt_25ms_flag ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_25ms <= 24'd0 ;else if(cnt_25ms == MAX_CNT25MS - 1)cnt_25ms <= 24'd0 ;else cnt_25ms <= cnt_25ms + 1'b1 ;endassign cnt_25ms_flag = (cnt_25ms == MAX_CNT25MS - 1) ;// led_out always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) led_out <= 2'd0 ;else if(cnt_25ms_flag)led_out <= ~led_out ;endendmodule// 流水

module led(input wire sys_clk ,input wire sys_rst_n ,output reg [1:0] led_out

);parameter MAX_CNT500MS = 25_000_000 ; // 0.5s 5000_0000 1sreg [25:0] cnt_1s ;// reg [25:0] cnt_1salways @(posedge sys_clk or negedge sys_rst_n) begin // �첽��λ����Ϊ���������¼���if(!sys_rst_n)cnt_1s <= 26'd0 ;else if(cnt_1s == MAX_CNT500MS - 1)cnt_1s <= 26'd0 ;else cnt_1s <= cnt_1s + 1'b1 ;end// reg [1:0] led_out always @(posedge sys_clk or negedge sys_rst_n) beginif(!sys_rst_n) led_out <= 2'b01 ;else if(cnt_1s == MAX_CNT500MS - 1)led_out <= ~led_out ;elseled_out <= led_out ;end

ila_0 your_instance_name (.clk ( sys_clk ) , // input wire clk.probe0 ( led_out ) , // input wire [1:0] probe0 .probe1 ( cnt_1s ) // input wire [25:0] probe1

);

endmodule

仿真代码:

`timescale 1ns/1ns

module test_led();reg sys_clk ;reg sys_rst_n ;wire [1:0] led_out ;led led_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.led_out ( led_out )

);parameter CYCLE = 20 ;defparam led_inst.MAX_CNT500MS = 25 ;initial beginsys_clk = 1'b1 ;sys_rst_n <= 1'b0 ;#(CYCLE * 5 ) ;sys_rst_n <= 1'b1 ;endalways #(CYCLE / 2) sys_clk = ~sys_clk ;endmodule查看全文

99%的人还看了

猜你感兴趣

版权申明

本文"ZYNQ_project:led":http://eshow365.cn/6-36679-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: android log能在release包里面打印吗

- 下一篇: CSS 动画特效运用目录