已解决

「Verilog学习笔记」位拆分与运算

来自网友在路上 183883提问 提问时间:2023-11-09 17:55:30阅读次数: 83

最佳答案 问答题库838位专家为你答疑解惑

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

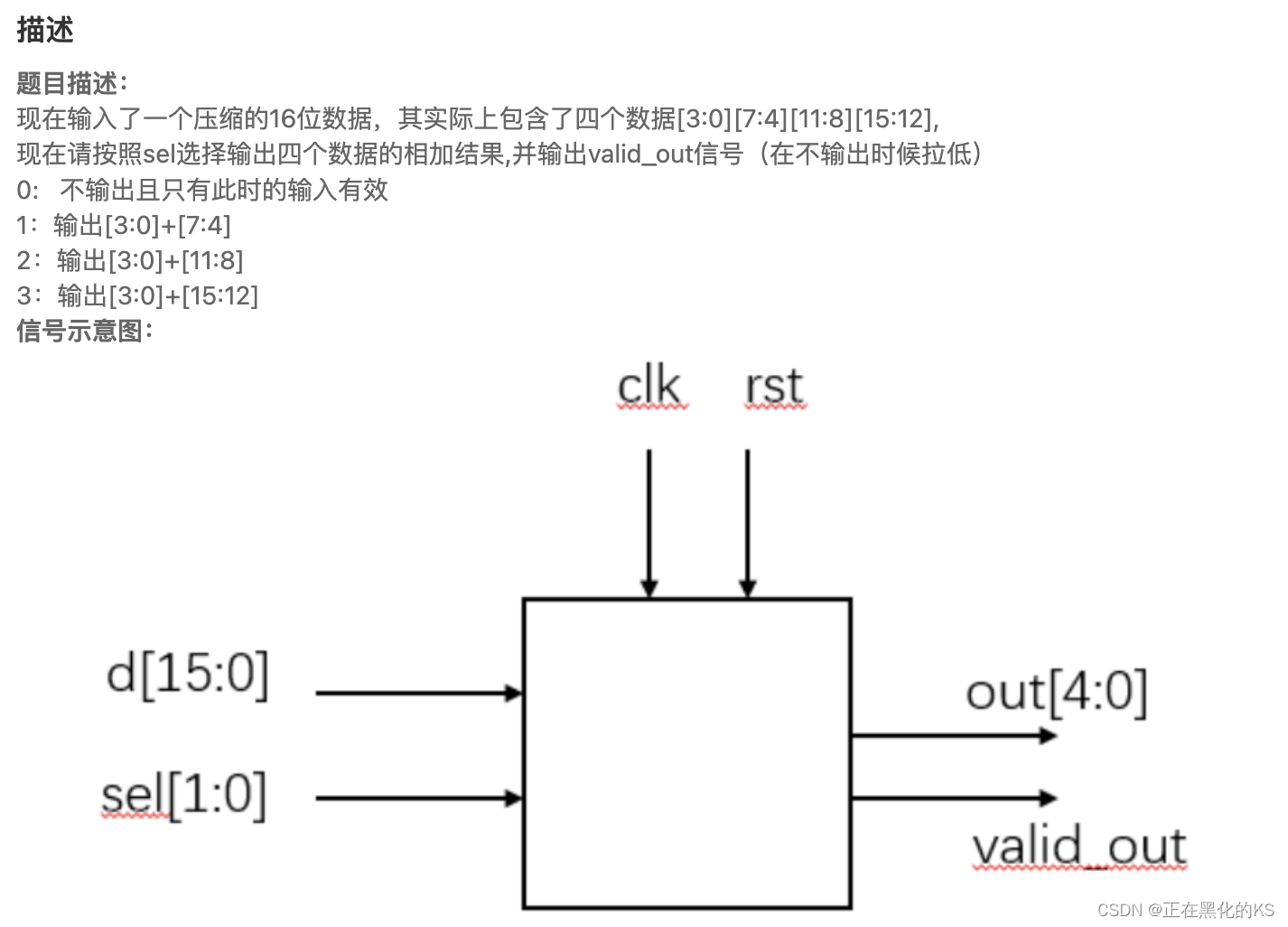

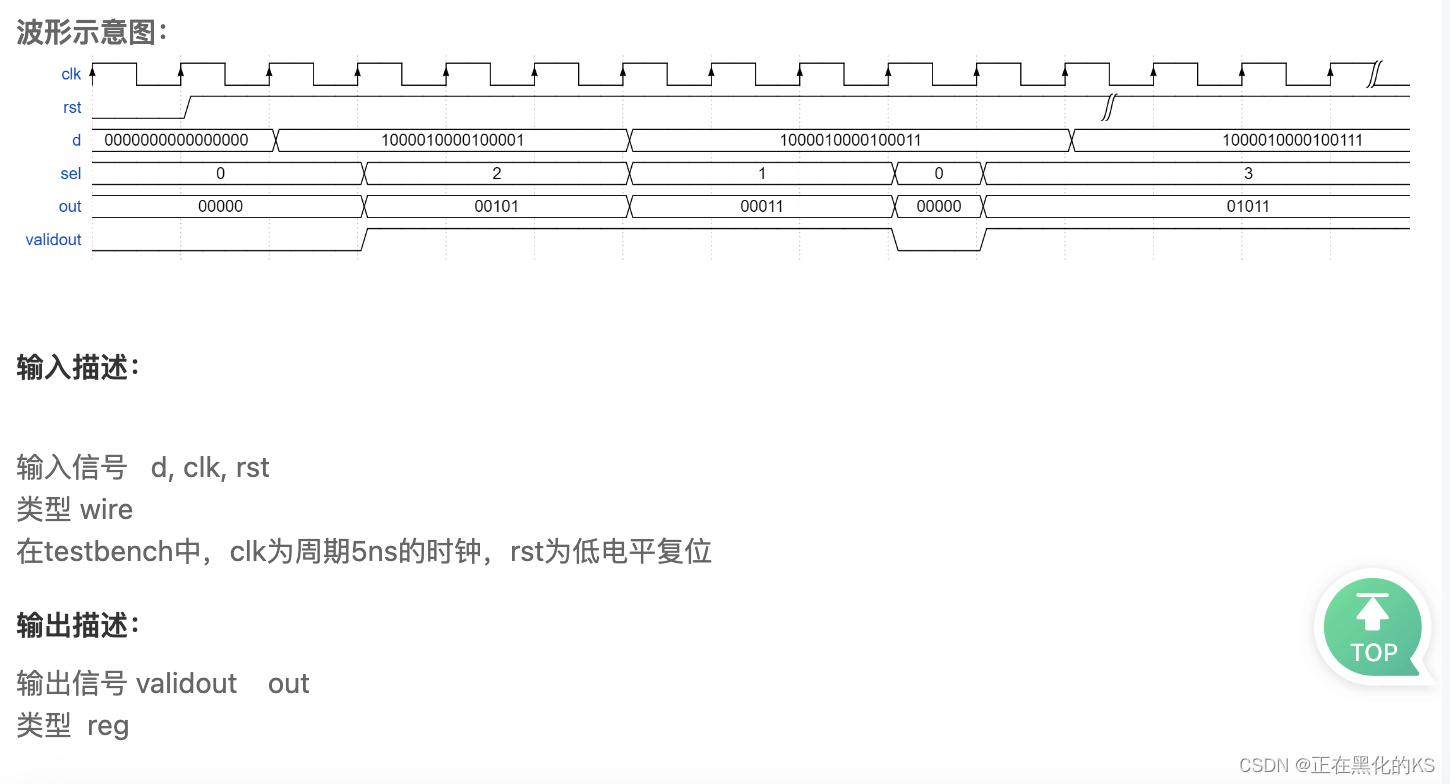

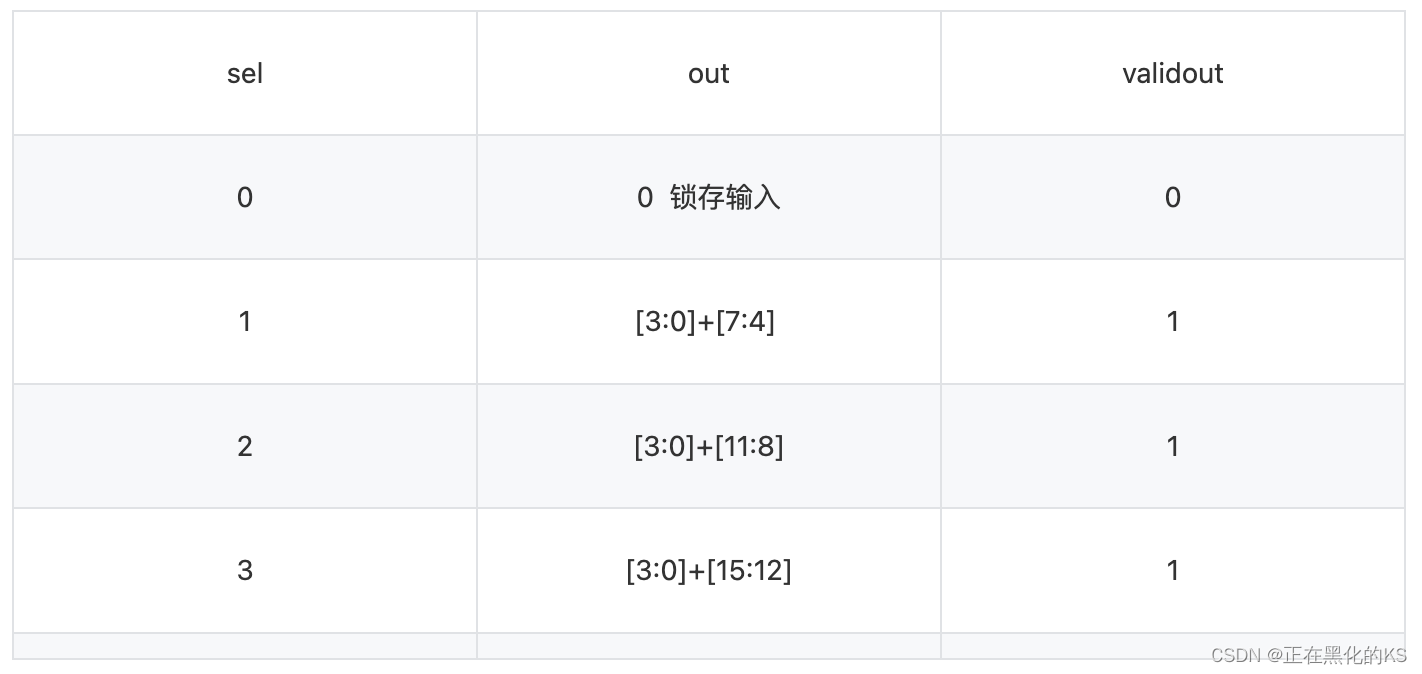

1、寄存器的位是可以分开单独运算的,并不是一个输入就一定是一个数据,在很多情况下,一个输入既包括数据又包括地址等其他有效信息

2、需要考虑数据锁存的问题,一定要在sel为0的时候进行锁存,只有此时的写入才是有效的(validout的下降沿写入有效),同时存在多种情况且没有优先级问题,建议使用case语句

`timescale 1ns/1nsmodule data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,output reg [4:0] out,

output reg validout

);

//*************code***********//reg [15:0] data_lock ; always @ (posedge clk or negedge rst) begin if (~rst) data_lock <= 0 ; else if (!sel) data_lock <= d ; end always @ (posedge clk or negedge rst) begin if (~rst) begin out <= 1'b0 ; validout <= 0 ; end else begin case (sel) 0 : begin out <= 1'b0 ; validout <= 0 ; end 1 : begin out <= data_lock[3:0] + data_lock[7:4] ; validout <= 1 ; end 2 : begin out <= data_lock[3:0] + data_lock[11:8] ; validout <= 1 ; end 3 : begin out <= data_lock[3:0] + data_lock[15:12] ;validout <= 1 ; end endcase end end //*************code***********//

endmodule

查看全文

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"「Verilog学习笔记」位拆分与运算":http://eshow365.cn/6-36392-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!