已解决

verilog 每日一练- 移位寄存器

来自网友在路上 11018101提问 提问时间:2023-11-05 20:35:22阅读次数: 101

最佳答案 问答题库1018位专家为你答疑解惑

module shift_1x64 (clk, shift,sr_in,sr_out,);input clk, shift;input sr_in;output sr_out;reg [63:0] sr;always@(posedge clk)beginif (shift == 1'b1)beginsr[63:1] <= sr[62:0];sr[0] <= sr_in;endendassign sr_out = sr[63];endmodule

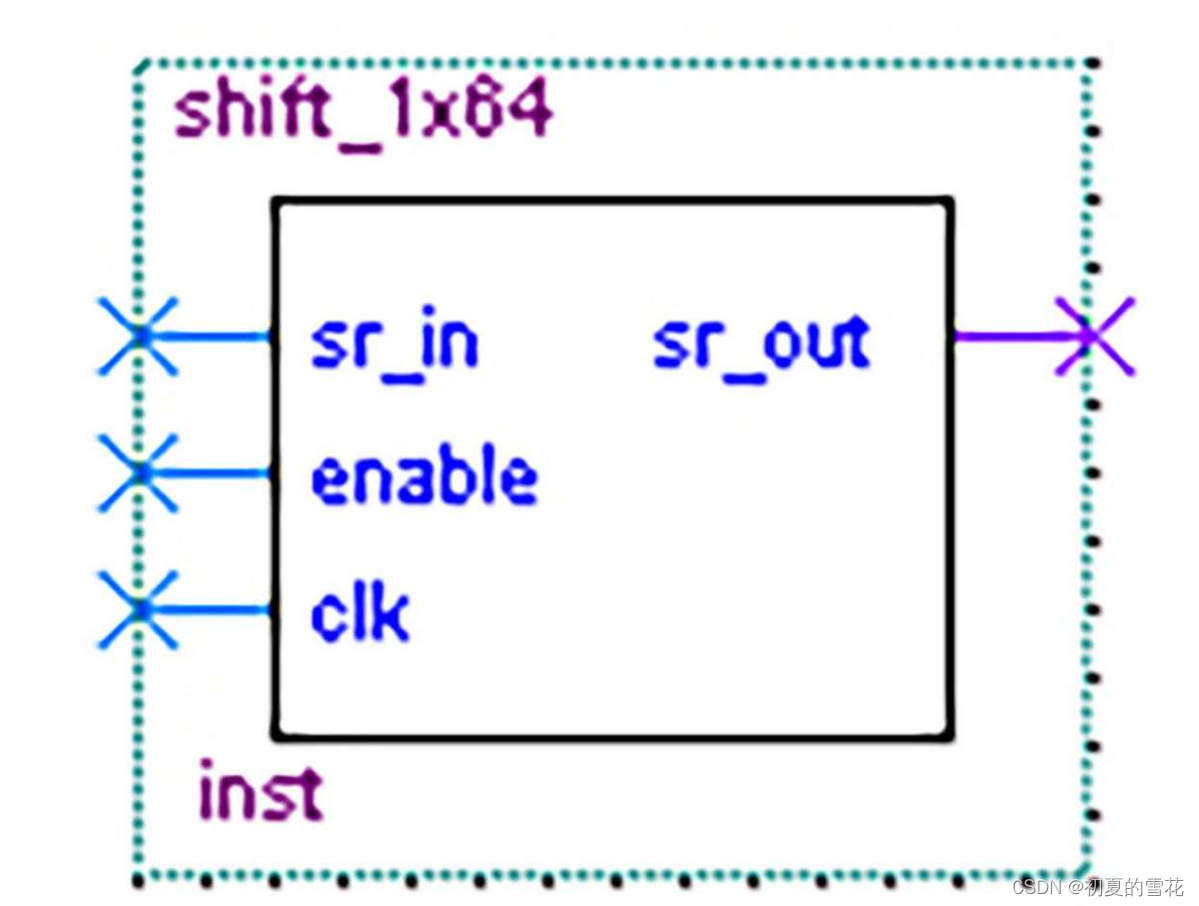

这个Verilog模块 `shift_1x64` 实现了一个 64 位移位寄存器,它具有以下关键特性:

1. 时钟触发:移位操作是由外部时钟信号 `clk` 上升沿触发的。

2. 移位控制:移位操作由 `shift` 信号控制,当 `shift` 为高电平(1)时,移位操作执行。

3. 数据输入:可以通过 `sr_in` 输入新的数据,该数据会在移位操作时加载到寄存器的最低位。

4. 数据输出:模块的输出 `sr_out` 是移位寄存器的最高位(Bit 63)的值。

5. 移位操作:在移位操作触发时,寄存器内的数据会向左移动一位,最高位的数据被丢弃,最低位被加载新的 `sr_in` 数据。

这个模块允许你在时钟上升沿触发时执行数据的左移位操作,并通过 `sr_in` 输入新的数据,以便在移位后将其加载到寄存器的最低位。同时,你可以通过 `sr_out` 输出寄存器的最高位的值。

查看全文

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"verilog 每日一练- 移位寄存器":http://eshow365.cn/6-32984-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: STM32WB55开发(6)----FUS更新

- 下一篇: UWB 技术在机器人和移动领域的应用题】