PCIe架构的处理器系统介绍

最佳答案 问答题库768位专家为你答疑解惑

不同的处理器系统中,PCIe体系结构的实现方式不尽相同。PCIe体系结构以Intel的x86处理器为蓝本实现,已被深深地烙下x86处理器的印记。在PCIe总线规范中,有许多内容是x86处理器独有的,也仅在x86处理器的Chipset中存在。在PCIe总线规范中,一些最新的功能也在Intel的Chipset中率先实现。本节将以一个处理器系统为例简要介绍RC的实现,并简单归纳RC的通用实现机制。

处理器系统

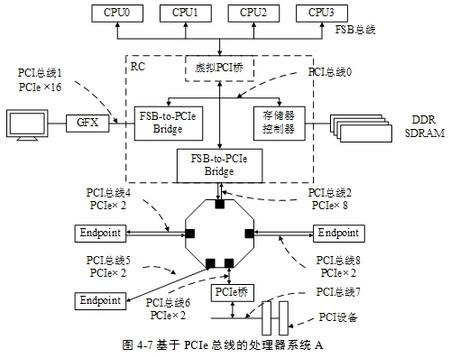

在有些处理器系统中,没有直接提供PCI总线,此时需要使用PCIe桥,将PCIe链路转换为PCI总线之后,才能连接PCI设备。在PCIe体系结构中,也存在PCI总线号的概念,其编号方式与PCI总线兼容。一个基于PCIe架构的处理器系统如图所示。

在上图的结构中,处理器系统首先使用一个虚拟的PCI桥分离处理器系统的存储器域与PCI总线域。FSB总线下的所有外部设备都属于PCI总线域。与这个虚拟PCI桥直接相连的总线为PCI总线0。这种架构与Intel的x86处理器系统较为类似。

在这种结构中,RC由两个FSB-to-PCIe桥和存储器控制器组成。值得注意的是在图4 7中,虚拟PCI桥的作用只是分离存储器域与PCI总线域,但是并不会改变信号的电气特性。RC与处理器通过FSB连接,而从电气特性上看,PCI总线0与FSB兼容,因此在PCI总线0上挂接的是FSB-to-PCIe桥,而不是PCI-to-PCIe桥。

在PCI总线0上有一个存储器控制器和两个FSB-to-PCIe桥。这两个FSB-to-PCIe桥分别推出一个×16和×8的PCIe链路,其中×16的PCIe链路连接显卡控制器(GFX),其编号为PCI总线1;×8的PCIe链路连接一个Switch进行PCIe链路扩展。而存储器控制器作为PCI总线0的一个Agent设备,连接DDR插槽或者颗粒。

此外在这个PCI总线上还可能连接了一些使用“PCI配置空间”管理的设备,这些设备的访问方法与PCI总线兼容,在x86处理器的Chipset中集成了一些内嵌的设备。这些内嵌的设备使用均使用“PCI配置空间”进行管理,包括存储器控制器。

PCIe总线使用端到端的连接方式,因此只有使用Switch才能对PCIe链路进行扩展,而每扩展一条PCIe链路将产生一个新的PCI总线号。如图4 7所示,Switch可以将1个×8的PCIe端口扩展为4个×2的PCIe端口,其中每一个PCIe端口都可以挂接EP。除此之外PCIe总线还可以使用PCIe桥,将PCIe总线转换为PCI总线或者PCI-X总线,之后挂接PCI/PCI-X设备。多数x86处理器系统使用这种结构连接PCIe或者PCI设备。

在PCIe总线规范中并没有明确提及PCIe主桥,而使用RC概括除了处理器之外的所有与PCIe总线相关的内容。在PCIe体系结构中,RC是一个很模糊也很混乱的概念。Intel使用PCI总线的概念管理所有外部设备,包括与这些外部设备相关的寄存器,因此在RC中包含一些实际上与PCIe总线无关的寄存器。使用这种方式有利于系统软件使用相同的平台管理所有外部设备,也利于平台软件的一致性,但是仍有其不足之处。

99%的人还看了

相似问题

- 基于STC12C5A60S2系列1T 8051单片机的IIC总线器件24C02记录单片机上电次数应用

- 电子电器架构 —— 车载网关边缘节点总线转换

- FPGA与STM32_FSMC总线通信实验

- LabVIEW在OPC中使用基金会现场总线

- 【CAN总线】从数字设计的角度分析CAN协议1—CAN概述

- CCLINK IEFB总线转ETHERNET/IP网络的协议网关使欧姆龙和三菱的数据互通的简单配置方法

- CAN(Controller Area Network)是一种用于在汽车和工业领域中进行通信的串行总线系统(附加案例)

- 企业服务总线ESB有什么作用?和微服务有什么区别?会如何发展?

- 传统汽车总线CAN(FD) LIN学习大纲

- 国产CAN总线收发芯片DP1042 兼容替换TJA1042

猜你感兴趣

版权申明

本文"PCIe架构的处理器系统介绍":http://eshow365.cn/6-26500-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!