已解决

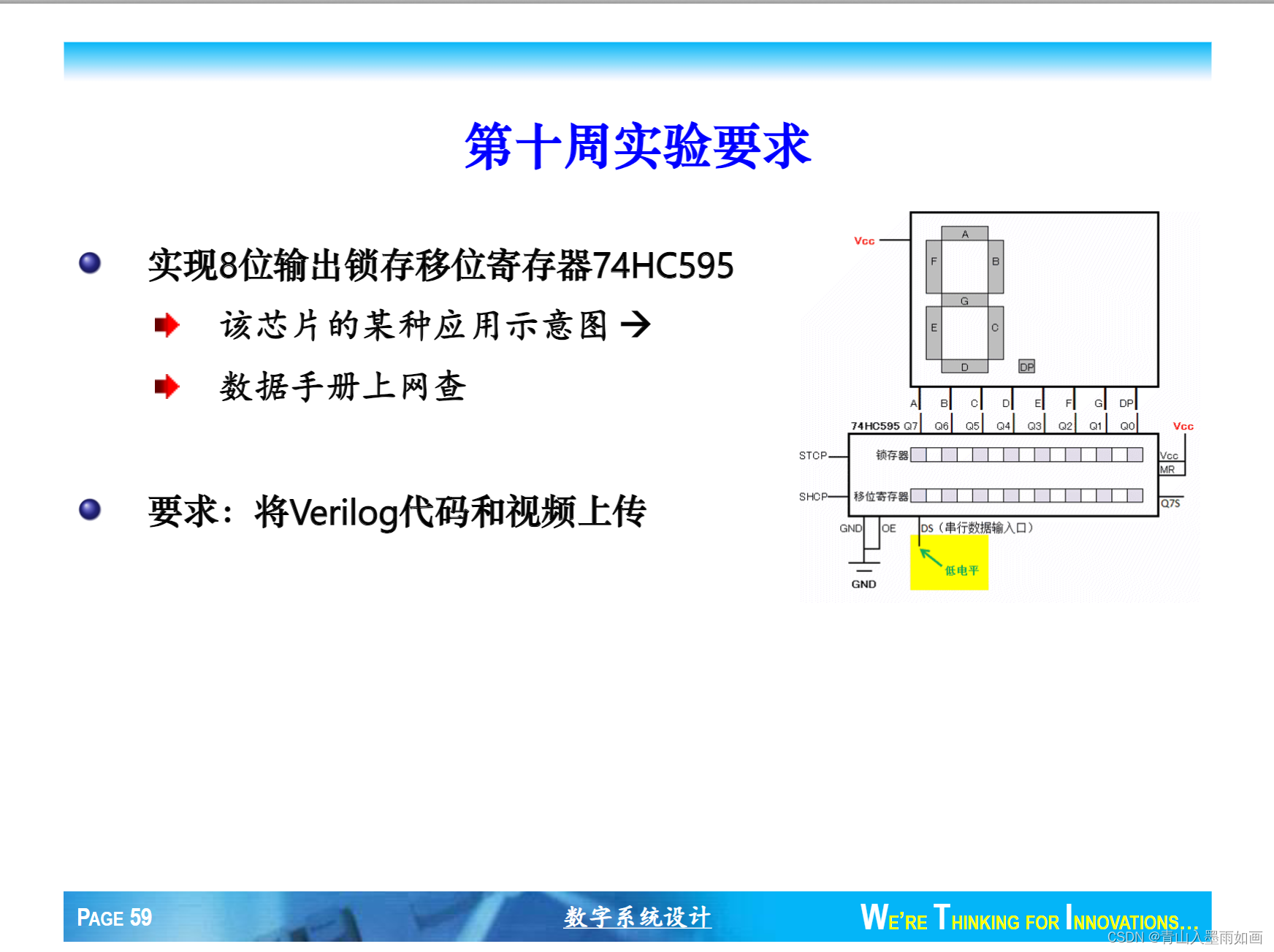

北邮22级信通院数电:Verilog-FPGA(10)第十周实验 实现移位寄存器74LS595

来自网友在路上 11148114提问 提问时间:2023-11-19 07:27:42阅读次数: 114

最佳答案 问答题库1148位专家为你答疑解惑

北邮22信通一枚~

跟随课程进度更新北邮信通院数字系统设计的笔记、代码和文章

持续关注作者 迎接数电实验学习~

获取更多文章,请访问专栏:

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

目录

一.代码部分

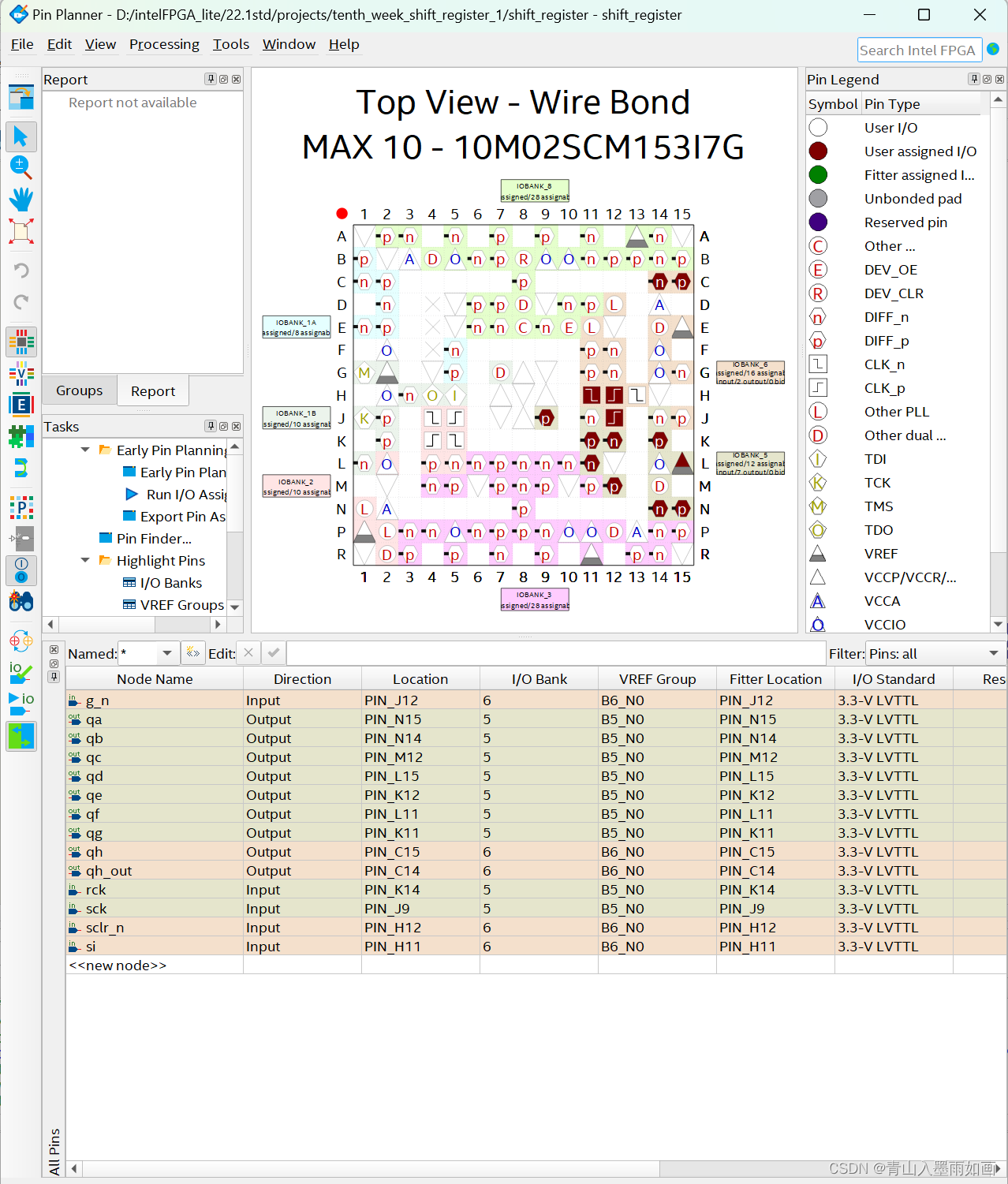

二.管脚分配

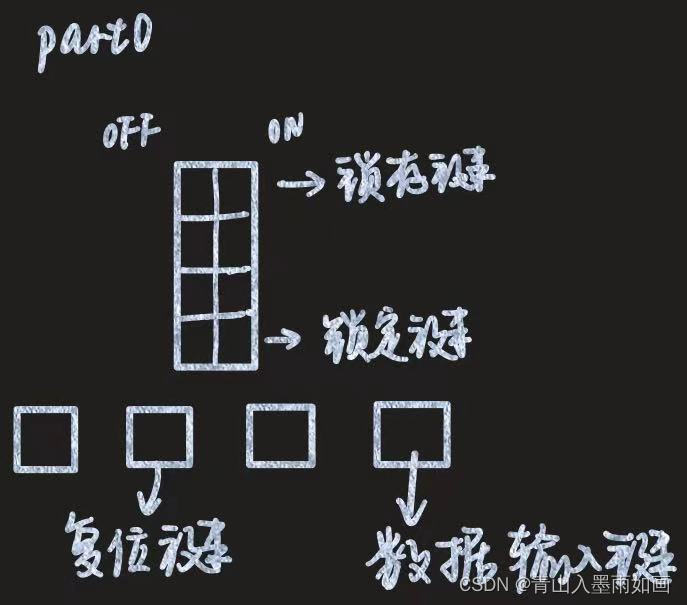

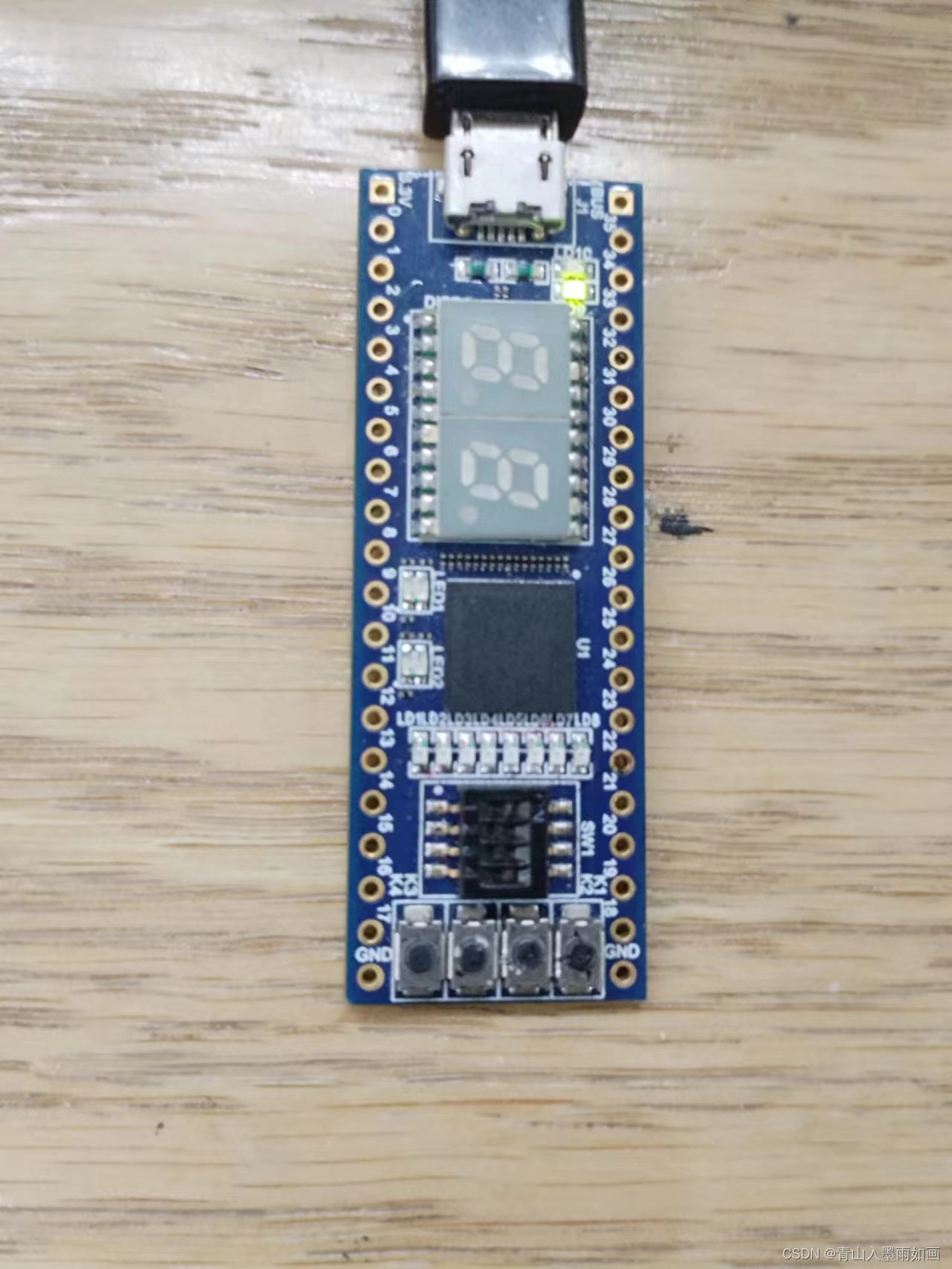

三.实现过程讲解及效果

一.代码部分

shift_register.v

module shift_register

(input sclr_n,si,sck,rck,g_n,output qa,qb,qc,qd,qe,qf,qg,qh,qh_out

);reg [7:0] shift_dffs;always@(posedge sck or negedge sclr_n)begin if(~sclr_n)shift_dffs[7:0]<=8'h00;elseshift_dffs[7:0]<={shift_dffs[6:0],si};endreg [7:0] storge_dffs;always @ (posedge rck)begin storge_dffs [7:0] <=shift_dffs[7:0];endassign qh_out=shift_dffs[7];assign {qh,qg,qf,qe,qd,qc,qb,qa} = g_n ? 8'bzzzz_zzzz : storge_dffs [7:0];

endmodule 二.管脚分配

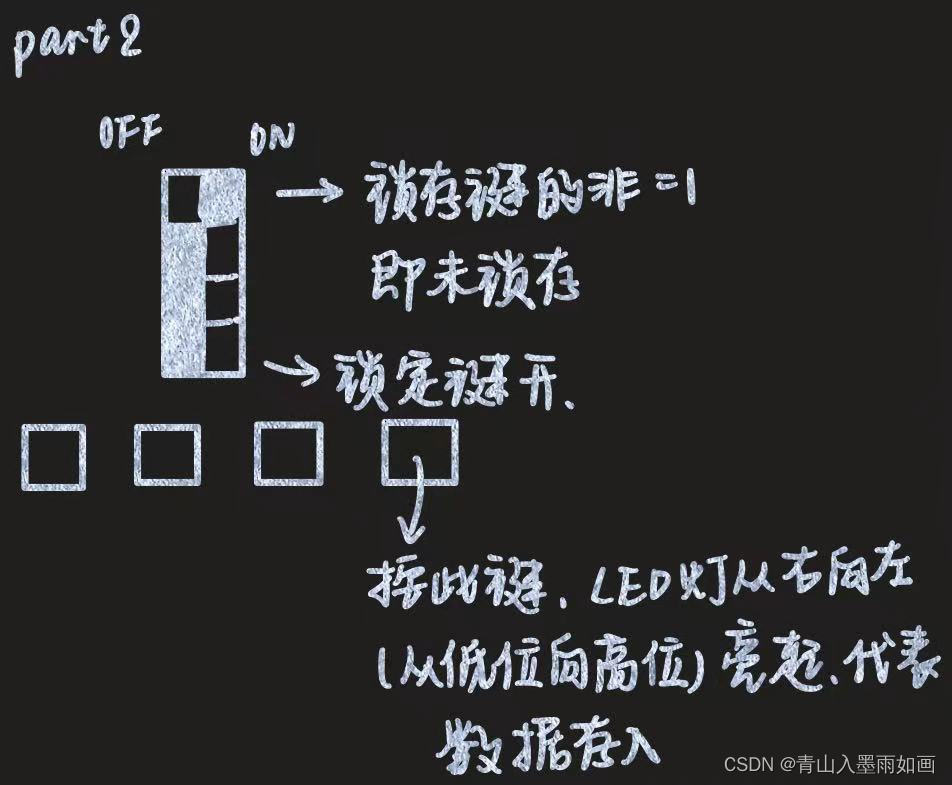

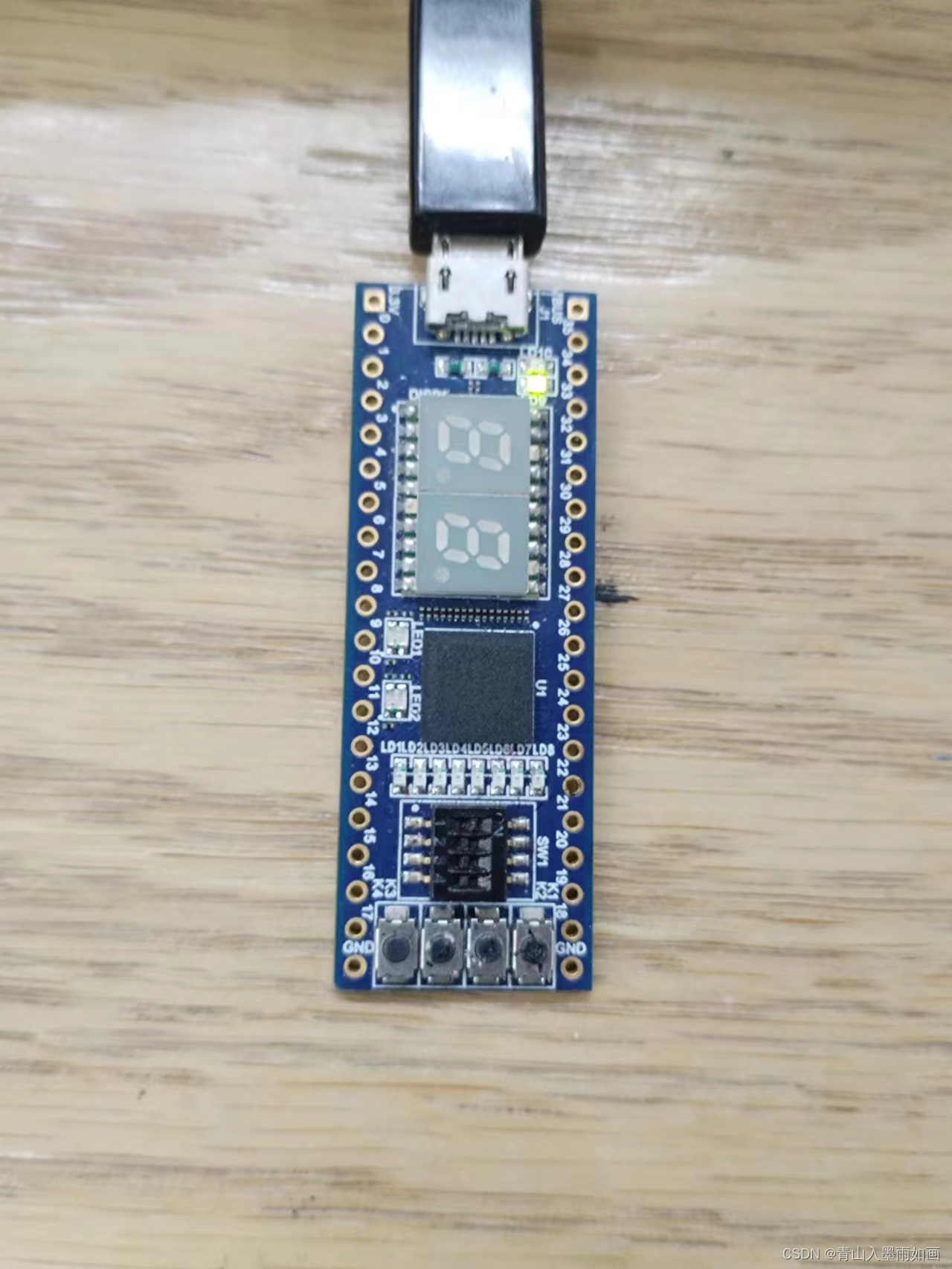

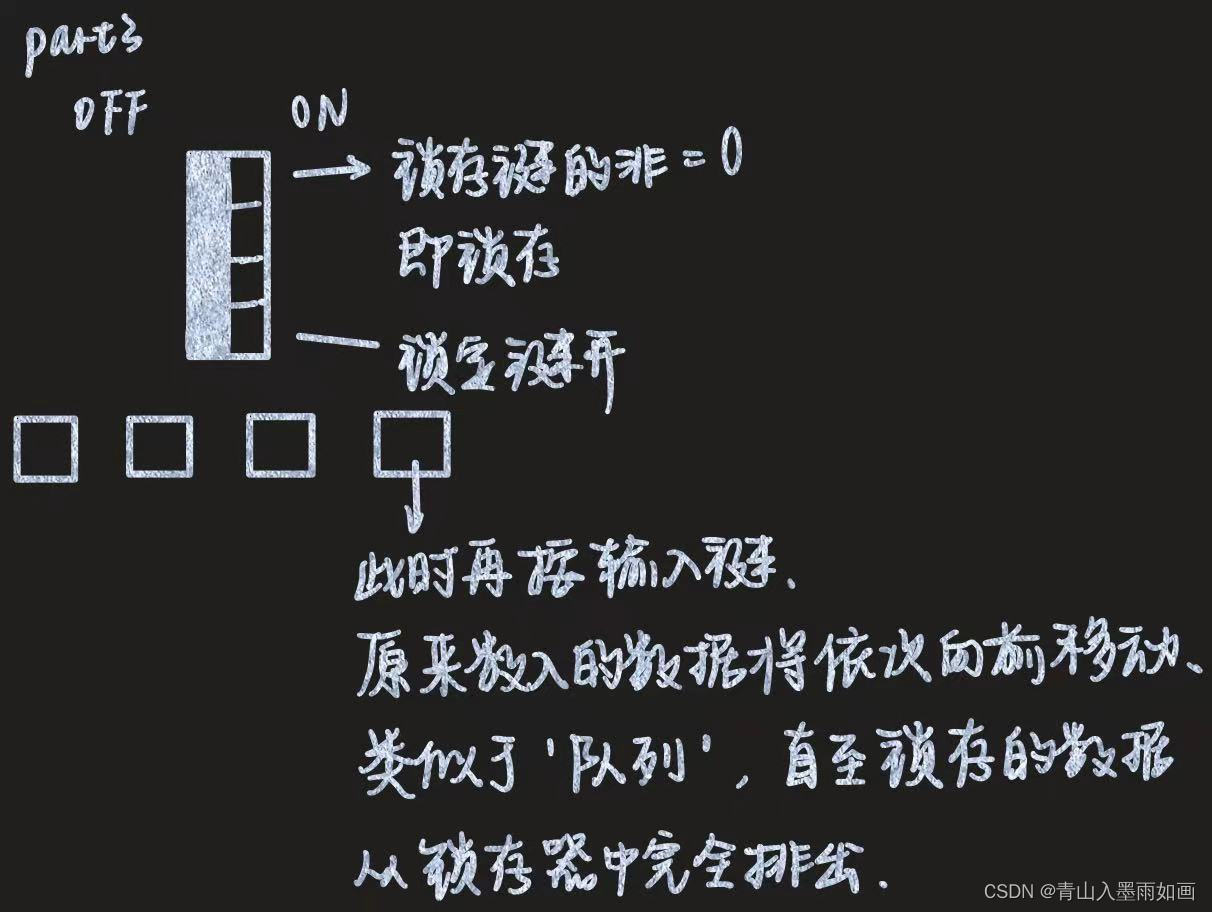

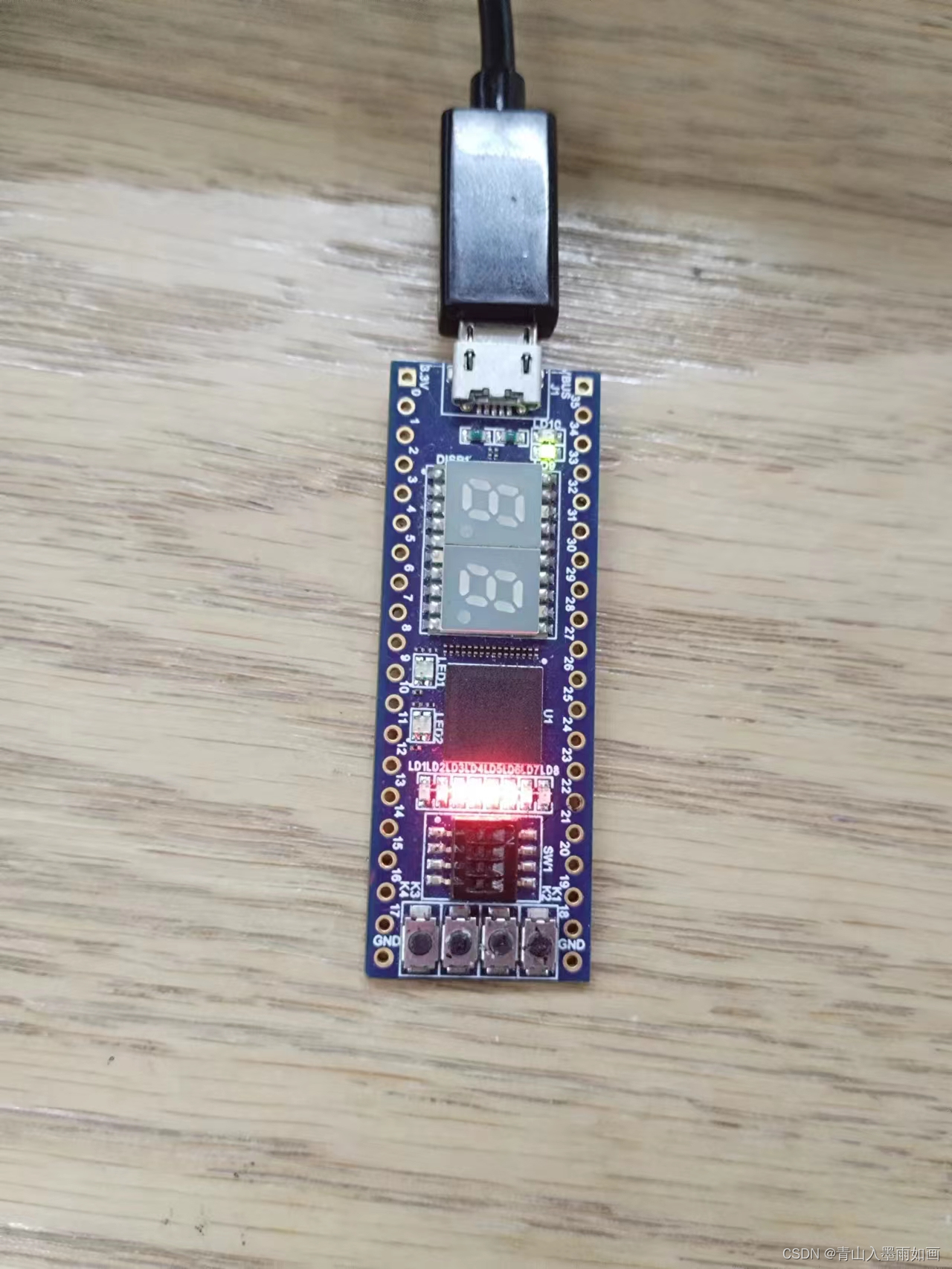

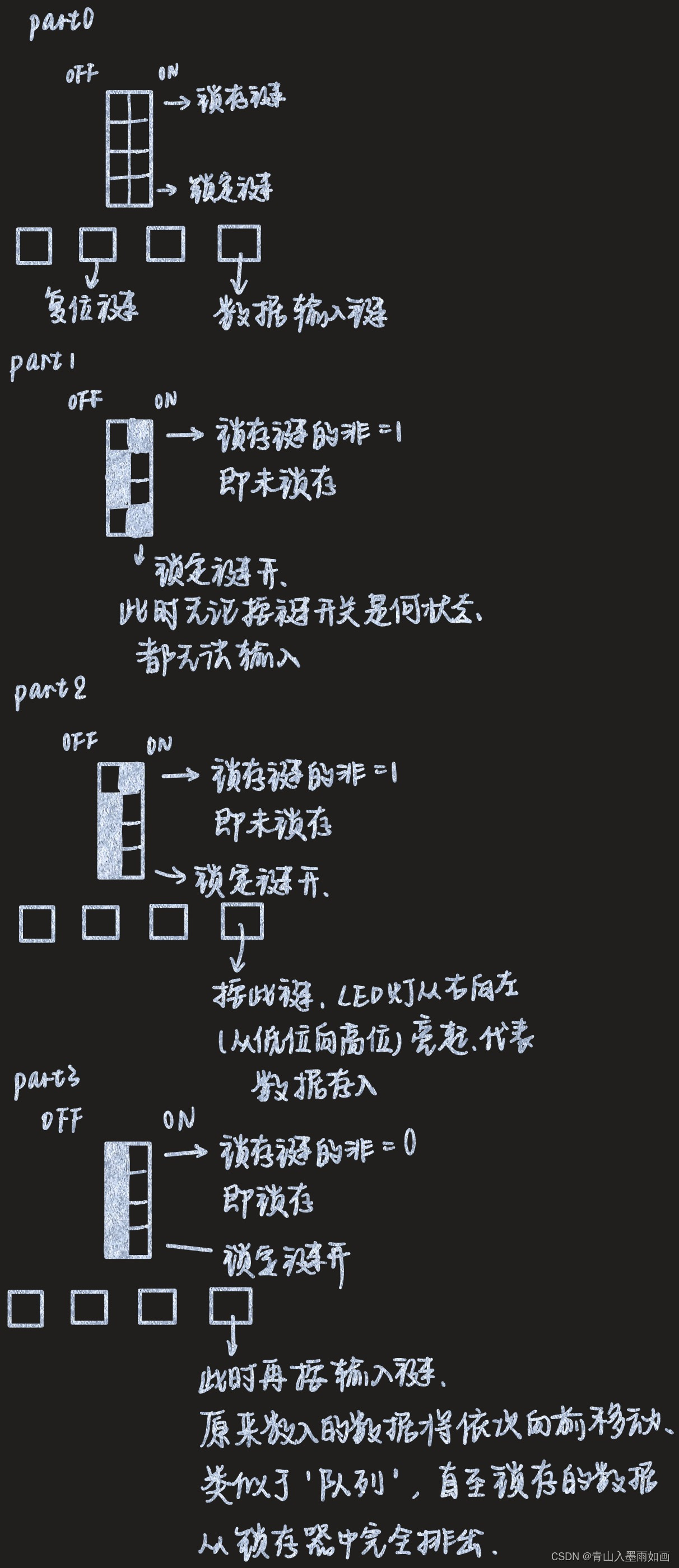

三.实现过程讲解及效果

查看全文

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"北邮22级信通院数电:Verilog-FPGA(10)第十周实验 实现移位寄存器74LS595":http://eshow365.cn/6-39021-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!