已解决

「Verilog学习笔记」异步复位的串联T触发器

来自网友在路上 11018101提问 提问时间:2023-11-04 13:40:18阅读次数: 101

最佳答案 问答题库1018位专家为你答疑解惑

专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

这道题目里我们有两个需要明确的点:

1. 什么是异步复位

2. 什么是串联的T触发器

关于第一个点,可以看我的这篇文章,已经整理好了:

「数字集成电路笔记」异步复位和同步复位的区别-CSDN博客

那么什么是串联的T触发器?

顾名思义,串联的T触发器就是两个T触发器相串联,第一个T触发器的输出会作为第二个T触发器的输入,对于一个T触发器,它的定义为:如果在时钟上升沿时刻,data为高电平,则输出为当前值的反转,即当前值为0,则会反转为1,反之则反转为0。从波形图我们可以看出最开始的当前值为0,rst一直为高电平,因此不会使T触发器复位。注意观察第65ns的波形图,此时处于时钟上升沿且data为高电平,此时第一个T触发器将输出q1从当前值为0翻转为1。在第75ns时,由于又到了时钟上升沿,此时q1作为第二个T触发器的输入,为高电平,因此第二个T触发器会翻转,因此输出q为1。同时,q1也需要翻转,因为data依然是高电平,因此q1此时变为0。

`timescale 1ns/1ns

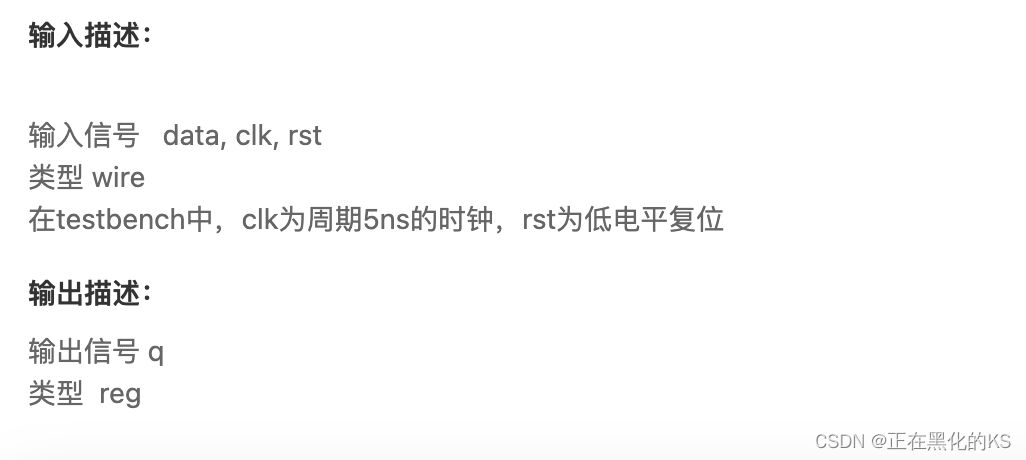

module Tff_2 (

input wire data, clk, rst,

output reg q

);

//*************code***********//reg q1 ; always @ (posedge clk or negedge rst)if (~rst) begin q1 <= 1'b0 ; q <= 1'b0 ; end else begin if (data) begin q1 <= !q1 ; end if (q1) begin q <= !q ; end end //*************code***********//

endmodule查看全文

99%的人还看了

相似问题

- SaleSmartly新增AI意图识别触发器!让客户享受更精准的自动化服务

- MySql跨库跨表触发器

- WPF中行为与触发器的概念及用法

- 使用Java语言实现基本RS触发器

- 06-MySQL-进阶-视图存储函数存储过程触发器

- 「Verilog学习笔记」异步复位的串联T触发器

- postgresql 触发器如何生成递增序列号,从1开始,并且每天重置

- PostgreSQL 17新特性之登录事件触发器

- 使用python操作mysql,,SQL注入问题, 视图, 触发器 ,事务(掌握重点), 存储过程,索引 问题

- python操作MySQL、SQL注入问题、视图、触发器、事务、存储过程、函数、流程控制、索引(重点)

猜你感兴趣

版权申明

本文"「Verilog学习笔记」异步复位的串联T触发器":http://eshow365.cn/6-31832-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!