计算机组成原理(五)

最佳答案 问答题库488位专家为你答疑解惑

十九、控制器

(一)分析各种指令过程,寻找控制单元作用

A、指令执行周期

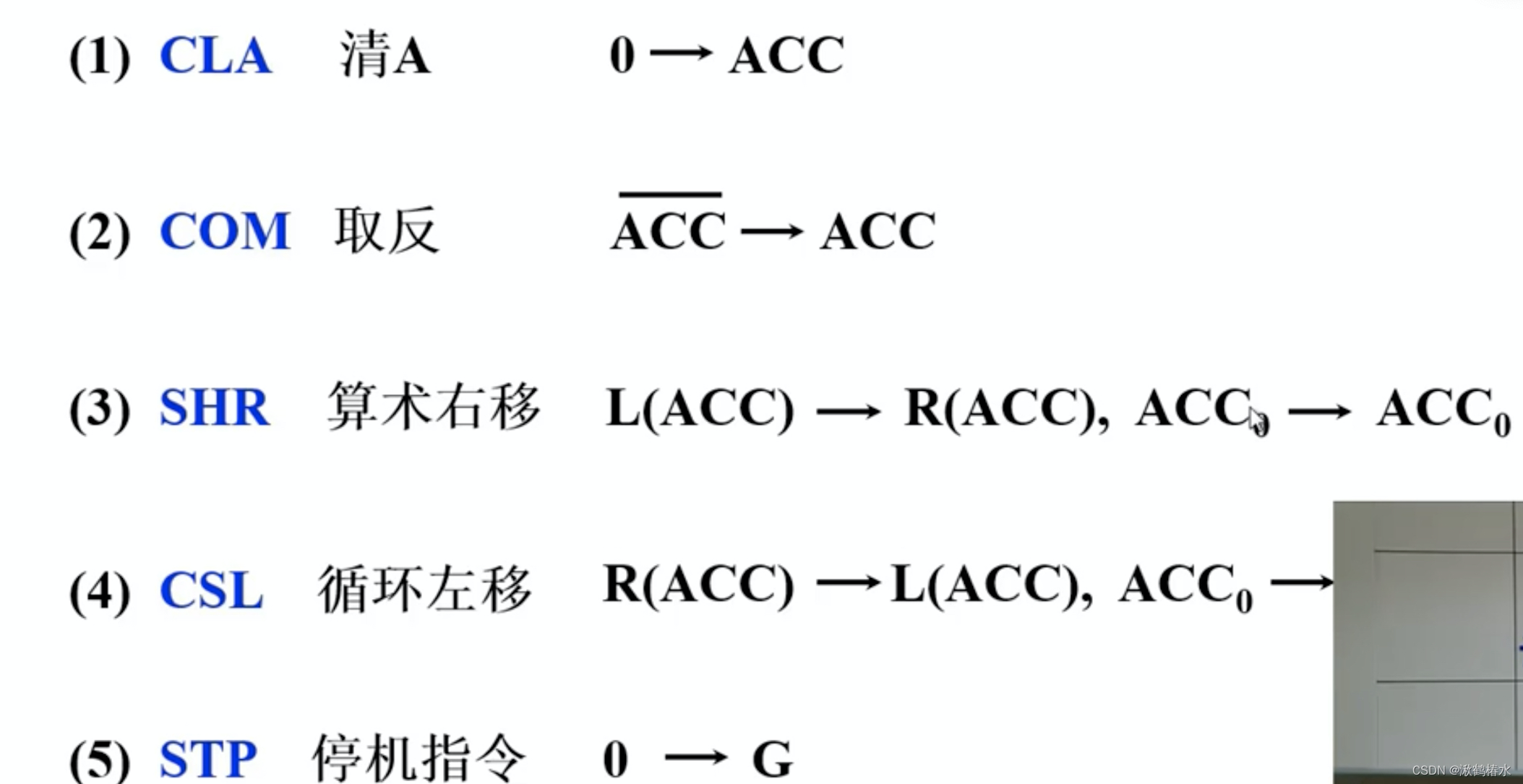

- 非访存指令(指令执行过程中,不需要访问内存即可操作),如下:

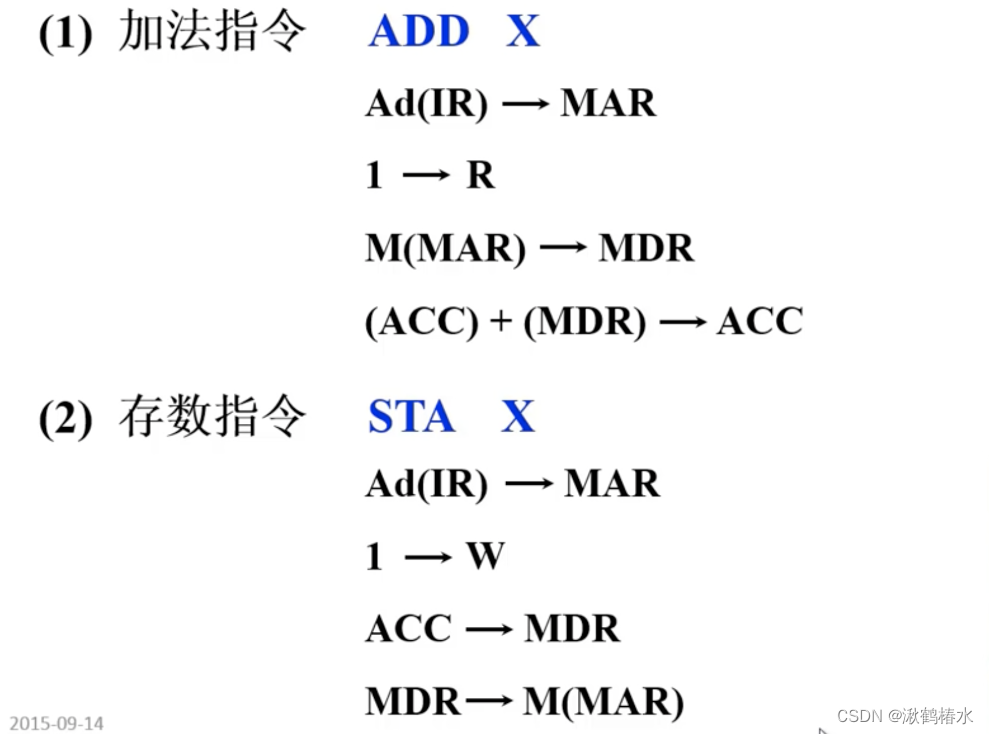

- 访存指令(指令执行过程中需哟啊访问内存),如下:

加法指令被取入IR中后,将自身的地址码从新送入MAR中,CU(控制器)发出读指令,内存将MAR中地址对应内容写入MDR中,返回给寄存器。

存术指令STA X,意味将寄存器内容存入指定X得地址对应存储单元。IR提供自身指令的操作数地址送入MAR,CU发出写命令,ACC写入MDR总,MDR再根据MAR中地址写入。

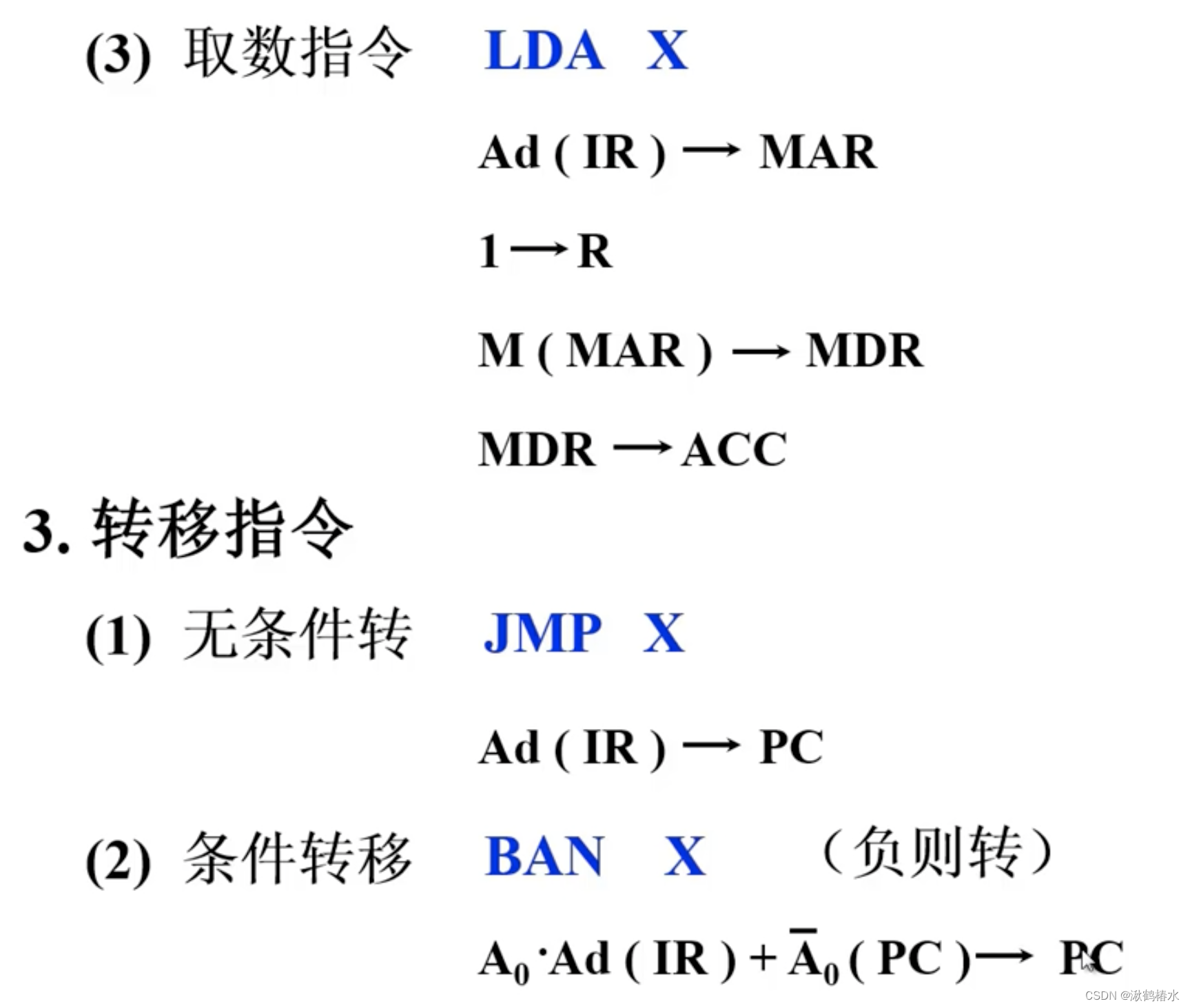

BAN指令,在执行周期中,要先查看ACC中上一条指令的运行结果的第一位(符号位)若为1(负)则将自己地址码送入PC作为下一条指令执行,如果为0,则保持原PC值迭代,自动执行下一条指令。

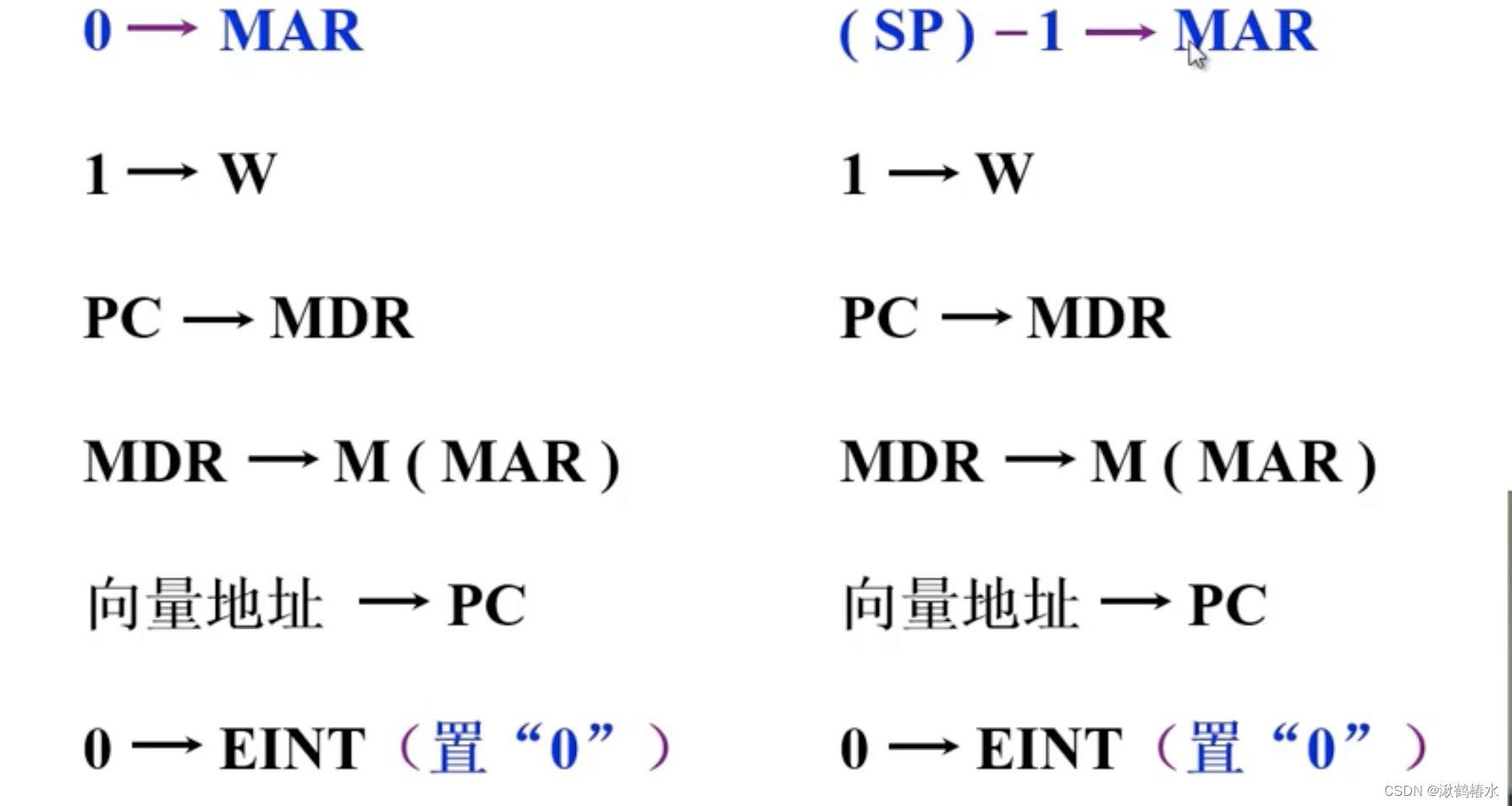

B、中断周期

程序断点存入0地址,0要送入MAR中,随后CU向存储器发出写命令W,然后PC(程序断点)送入MDR,MDR根据CU送入MAR中的0地址存入程序断点,而后向量生成中断程序入口地址送入PC或者中断识别程序送PC开始生成中断程序入口地址并执行。最后关中断。(断点存入存储器)

(断点入栈方式只有第一步不一样)SP(栈顶)-1,然后送入MAR,即一会送入MDR中的数据(断点)要保存的位置(栈顶)

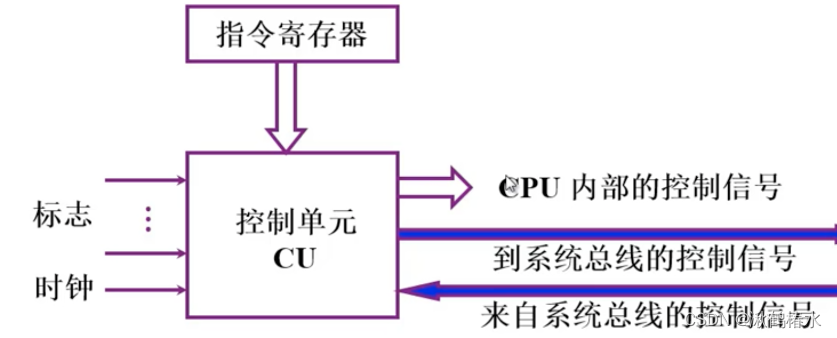

(二)控制器结构

A、控制器外部线路概览

- 时钟信号用来控制CU做周期性的运转。

- 标志用来获得某些结构的状态。

- 指令寄存器将指令的操作码部分送入CU。

- CPU内部控制信号,控制CPU内部其他各部件进行相关操作。

- 到系统总线的控制信号,用来控制计算机其他部件进行工作。

- 来自系统总线的控制信号,一般如中断请求信号等。

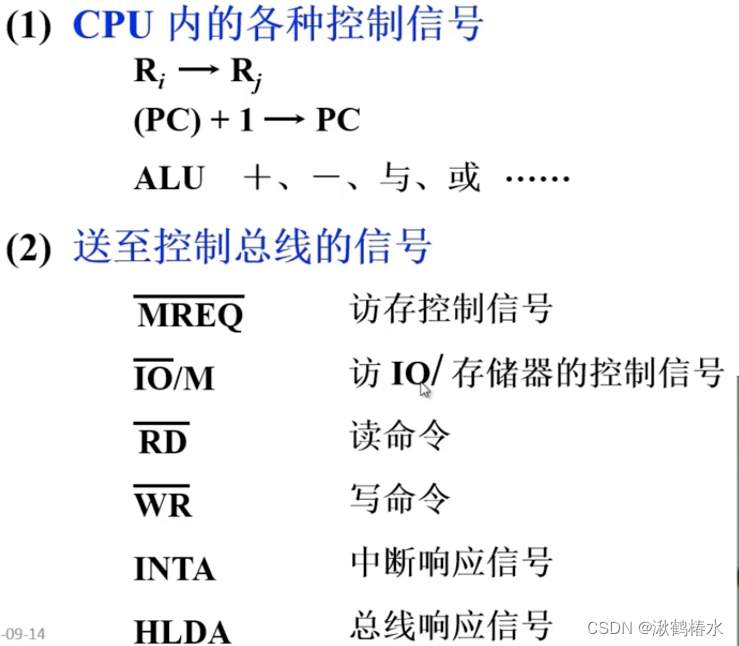

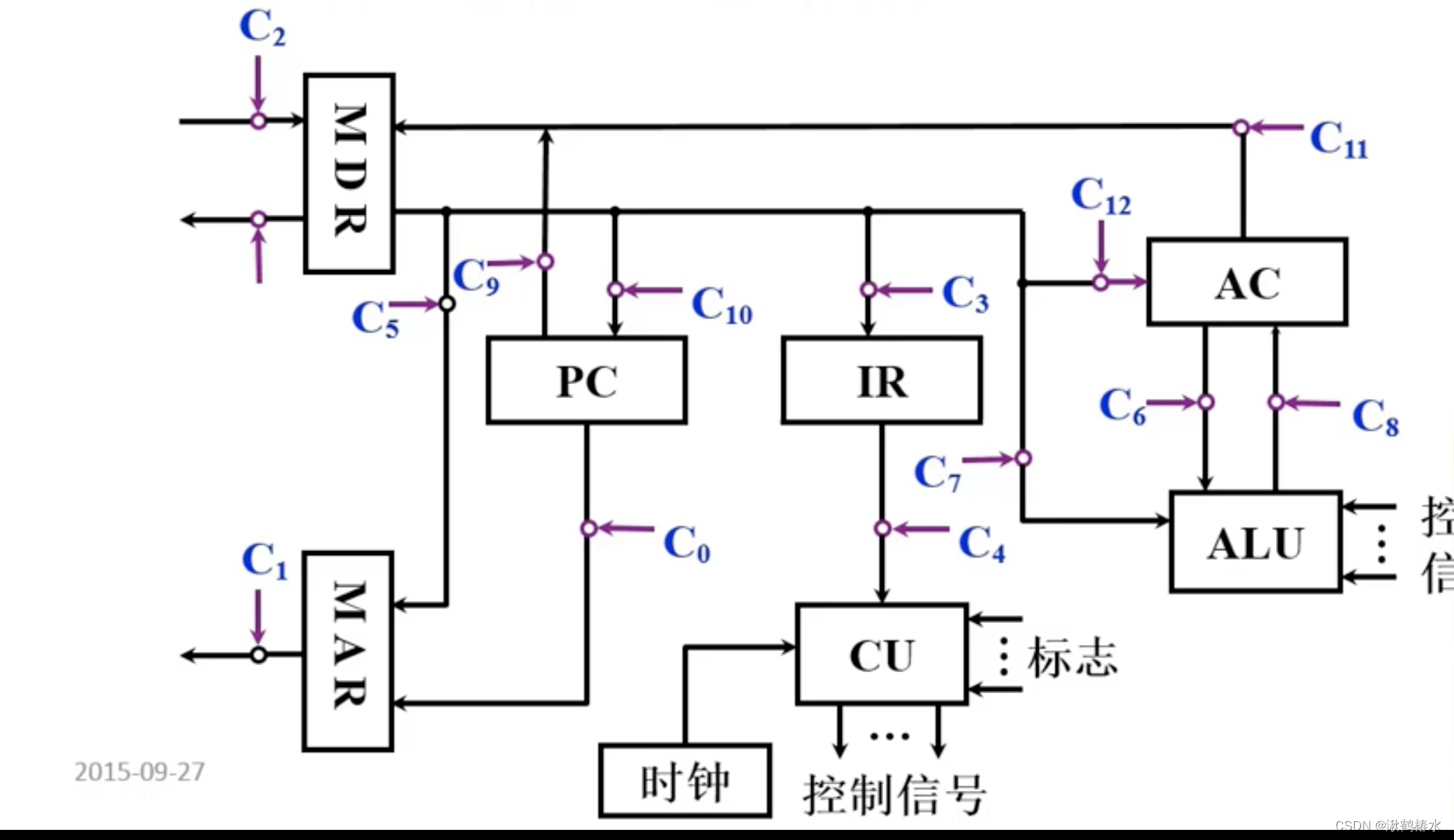

B、控制信号举例(不采用CPU内部总线,直接互联、以ADD指令为例)

- 取指周期

CU打开控制门C0,将PC中指令所在地址送入MAR,CU打开MAR到主存的控制门C1,同时向主存发出读命令,主存收到读命令后,通过C2控制门将指令送入MDR,MDR将ADD命令送入IR,同时将ADD命令中的一个操作数送入ACC寄存器中,然后IR将自己ADD的操作码送入CU进行解析。

- 执行周期

上一周期取出的指令还在MDR中,MDR将指令的地址码送入MAR(C5由CU控制打开),CU打开C1,将ADD需要的另一个操作数地址送入主存,同时发出读命令,主存收到读命令后,将操作数返回到MDR中,MDR将操作数送入ALU中,CU打开C6、C7,ALU将两个数相加得到结果送入ACC寄存器中。

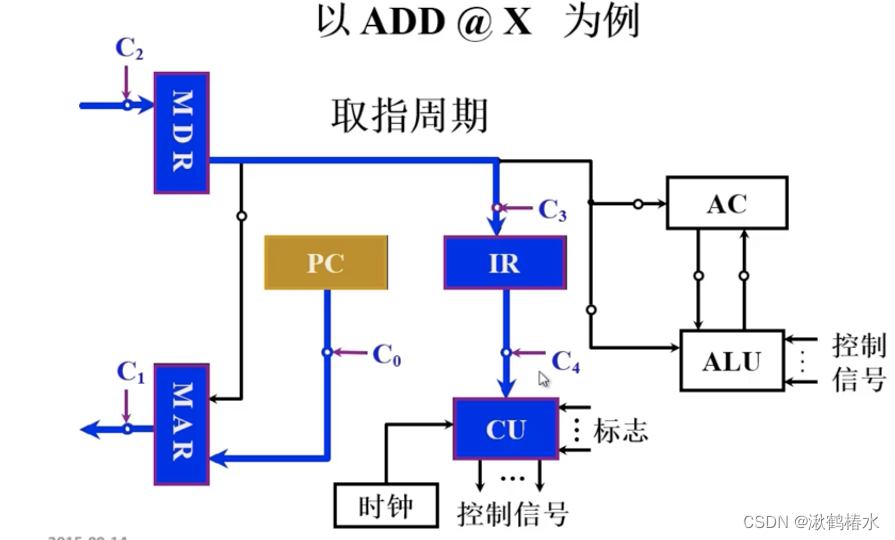

- 间址周期(如果ADD的地址码是形式地址)

MDR将其中的ADD指令的地址码(形式地址)送入MAR中,然后CU发出读信号,主存将形式地址对应的真实地址送入MDR,MDR将真实地址同步到IR中ADD指令的地址码部分。

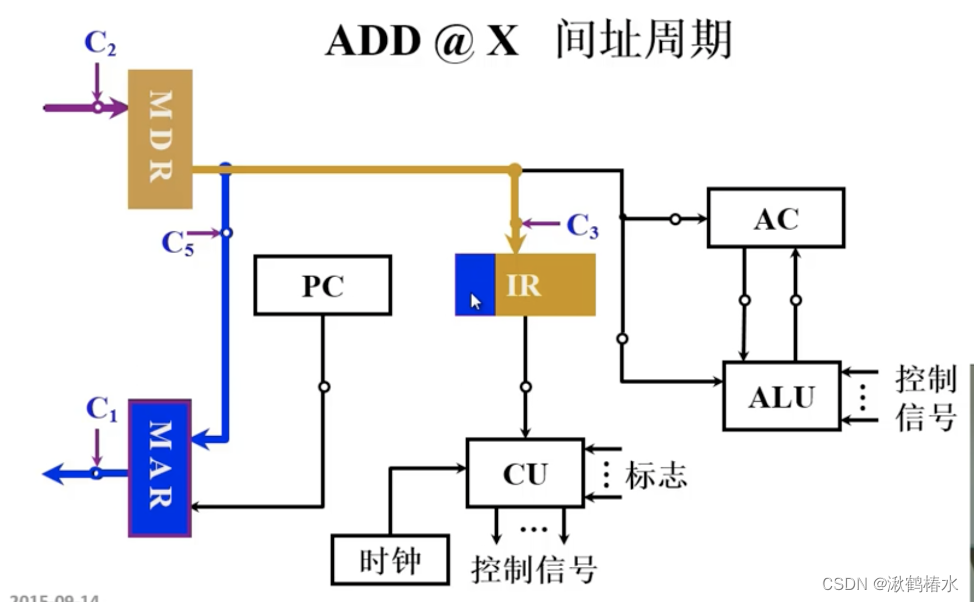

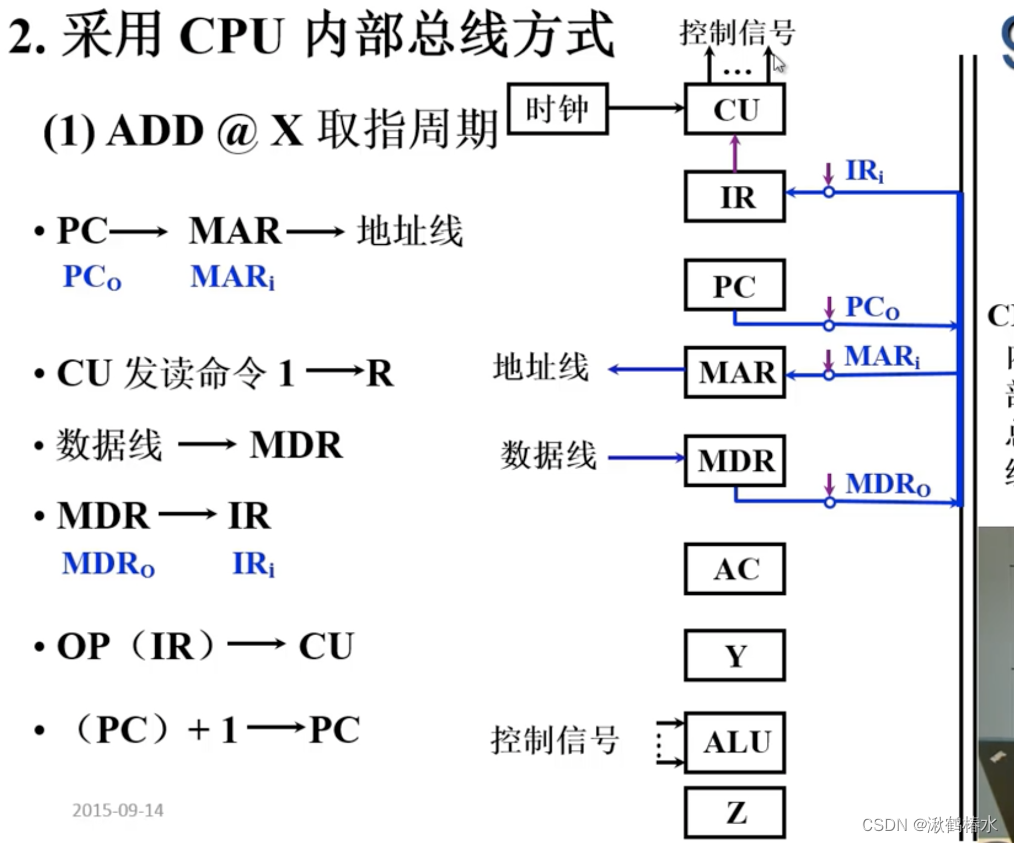

C、控制信号举例(使用CPU内部总线方式)

- 取指周期

CU将IR对应通路(IRi)打开PC将要获取指令的地址送入CPU总线,送入MAR中,CU通过控制总线向主存发出读命令,主存将指令内容通过数据总线返回到MDR,CU打开MDR0通路,MDR将指令通过总线送入IR(指令寄存器),IR通过IR和CU间的通路将指令的操作码部分送入CU供其解析。

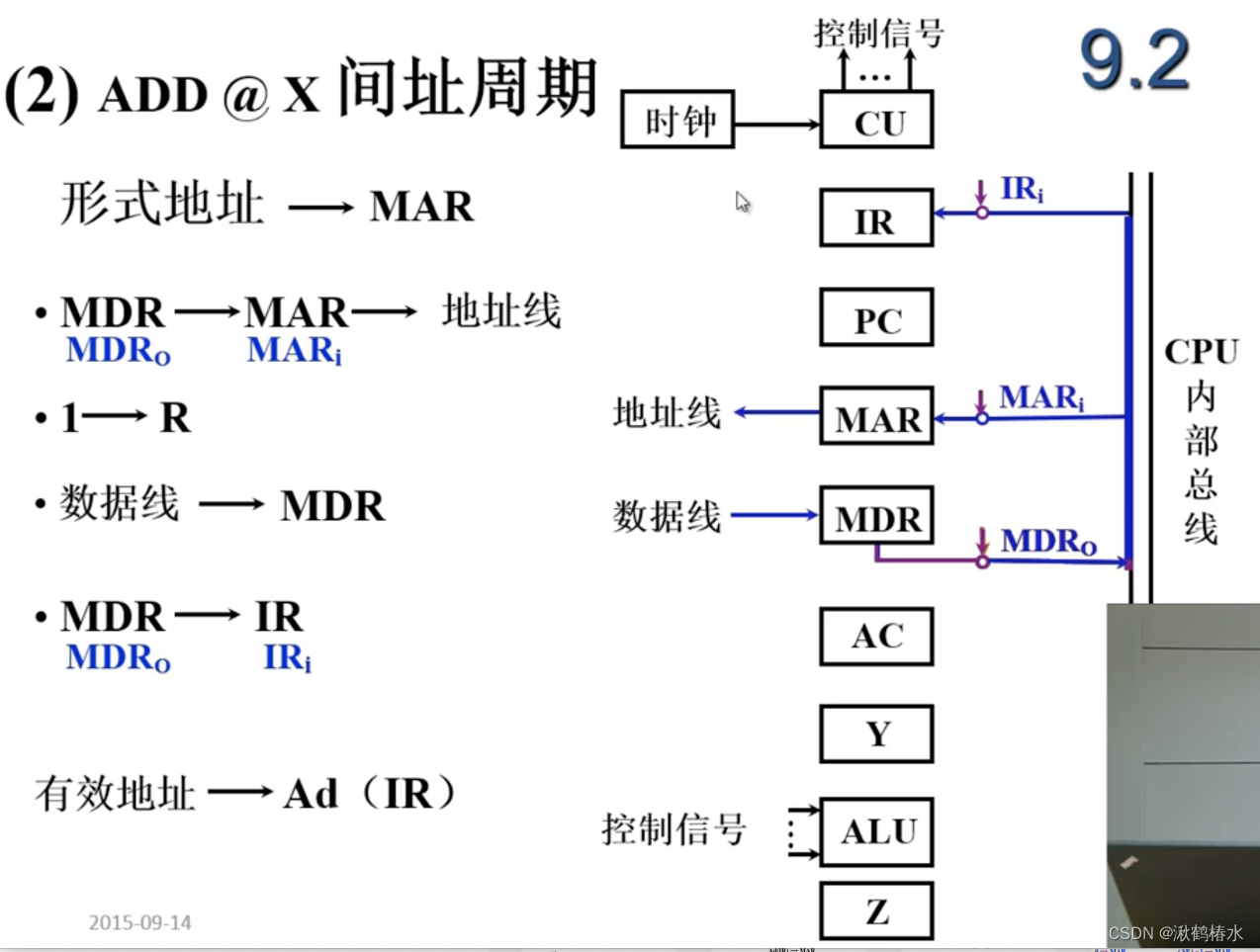

- 间址周期

如果操作数是通过间址寻址方式获得的话,当指令被送入MDR之后,MDR中的指令的地址码部分是形式地址,MDR会通过MDR0打开后的通路接入总线,将形式地址传入MAR,MAR再通过地址总线将地址传入主存, CU发出读命令,然后主存将真实操作码地址返回MDR中,MDR将新的地址码同步到指令中,用于执行阶段对操作数的获取。

- 执行周期

MDR将真实操作数地址通过CPU的内部总线(每次进入总线都需要CU打开相关门,以后都忽略)传入总线到达MAR中,MAR通过地址总线将地址传入主存,CU向主存发出读命令,主存收到读命令后,将数据通过数据总线返回到MDR中,MDR将数据通过总线传入Y中,随后CU(控制单元)发出ADD运算指令,AC、Y中操作数同时送入ALU中,运算结果保存在Z中,Z再通过总线传入ACC,ACC最终作为保存结果的位置。

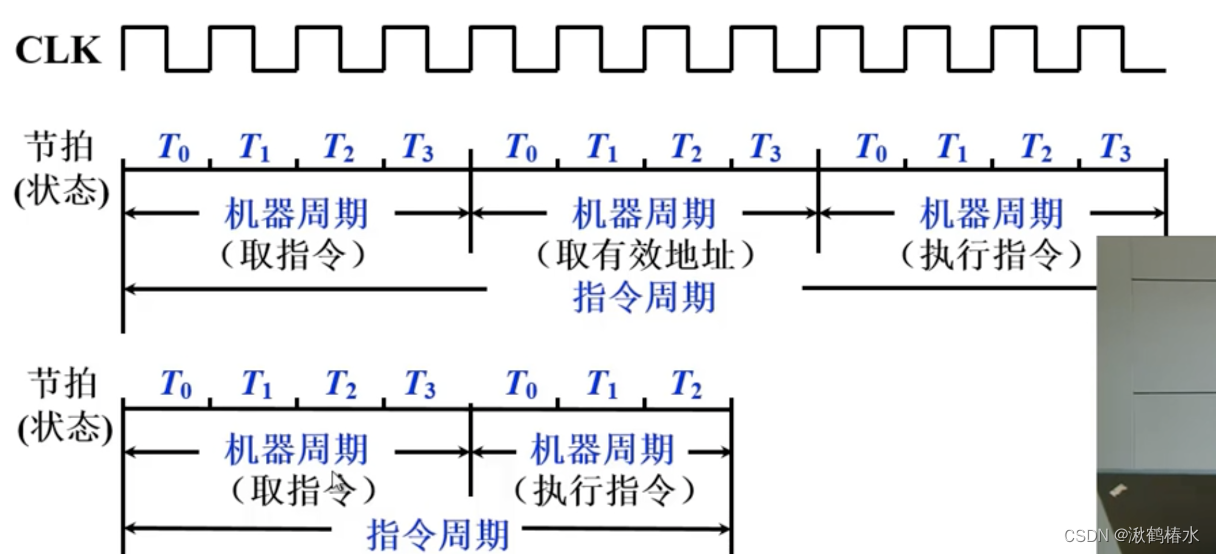

(三)多级时序系统

A、机器周期

- 机器周期:就是所有指令在执行的过程当中的一个基准时间,通俗来讲,我们之前看到的指令的不同阶段(周期)就是机器周期的上一级时序,指令周期由机器周期构成。

- 确定机器周期需要考虑的因素:每条指令执行的步骤,每一步骤所需的时间。

- 基准时间的确定,一般要用完成最复杂指令所需要的时间作为基准时间。一般指令中涉及要访问主存的指令用时最长,故我们可以以访问一次储存器的时间为基准。

- 如果指令字=储存字长,则取值周期=机器周期。

B、时钟周期(节拍、状态)

- 这一概念比机器周期小,机器周期是由多个时钟周期(节拍、状态)构成。例如我们在指令执行周期(机器周期)中,会将MAR中的地址送入主存,会将IR中的指令送入CU进行指令解释。

- 每个节拍是一个微操作。

- 时钟周期是计算机操作中的最小单位时间。

- 一个机器周期被分成若干个相等的节拍(时钟周期、状态)。

- 我们用时钟周期控制产生一个或几个微操作命令(多个命令可以同时在一个节拍下并行运行)。

C、机器周期和节拍构成的多级时序系统

如上图,一个指令周期包含多个机器周期,一个机器周期包含多个节拍。

每个机器周期包含的节拍数可以不同,也可以相同。

D、机器速度与机器主频的关系

机器的主频f越快,机器的速度越快,前提是机器周期中所含的节拍(主频的倒数)数以及指令周期中所含有的机器周期数有关。

在上面条件下,平均指令执行速度之比,就是两台机器的主频之比。

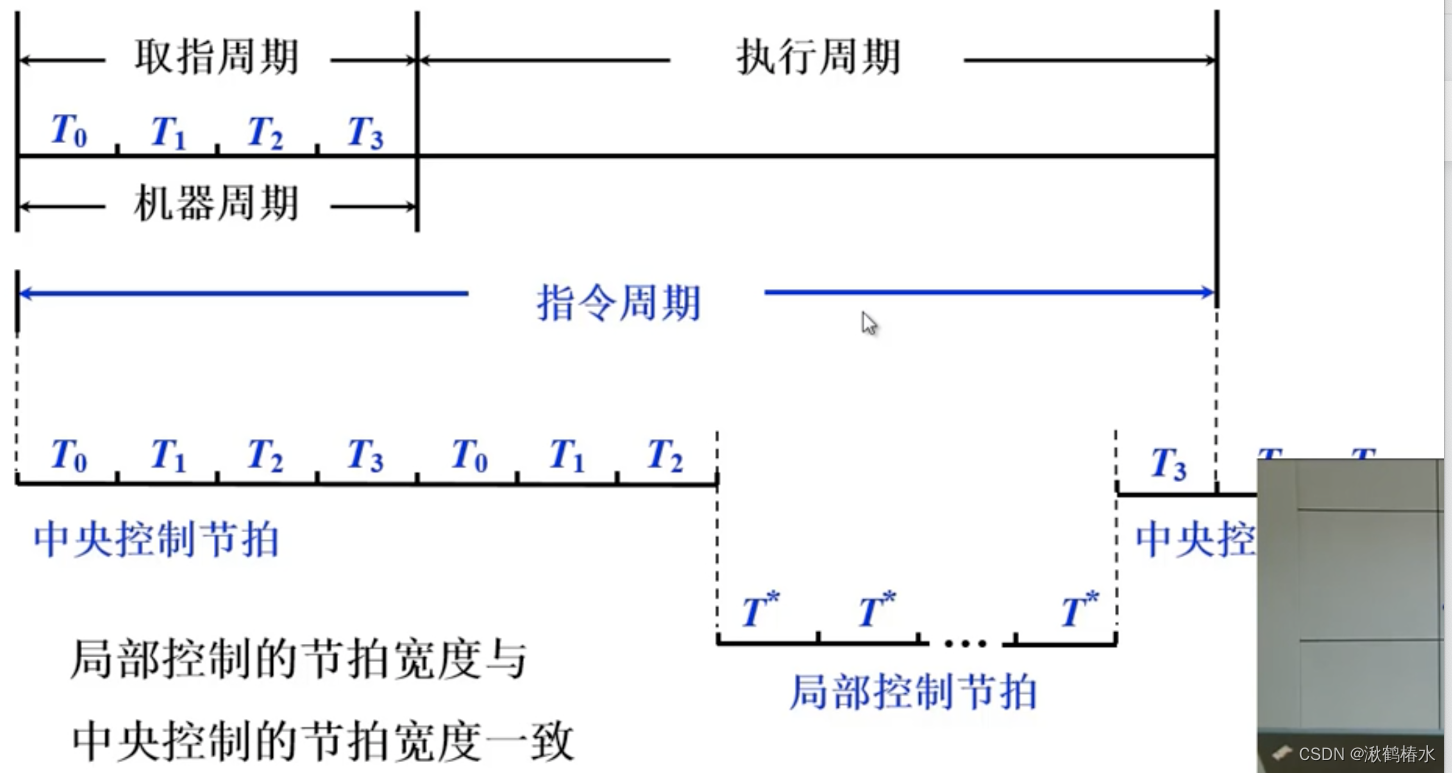

(四)控制方式

产生不同微操作命令序列所用的时序控制方式

A、同步控制的方式

每个节拍(微操作)都是由统一基准时标的信号控制。

- 实现方式一:采用定长的机器周期,用最长的微操作序列(可以暂理解为机器周期)和最复杂的微操作作为标准,机器周期内的节拍数相同。这样就导致一些简单的微操作序列,不需要太长时间,从而导致节拍闲置(浪费)。

- 可以通过延长一些机器周期(增加节拍)的方式来增加节拍利用率

- 采用中央控制和局部控制相结合的方法:(延长部分用局部控制节拍来控制)

B、异步方式

无基准时标信号;无固定的周期节拍和严格的时钟同步;采用应答方式(“相互握手”)

C、联合控制方式

同步和异步相结合。

D、人工干预方式(用于程序调控等)

RESET、连续和单条指令执行转换开关、符合停机开关。

(五)控制器的结构设计

A、组合控制逻辑方式

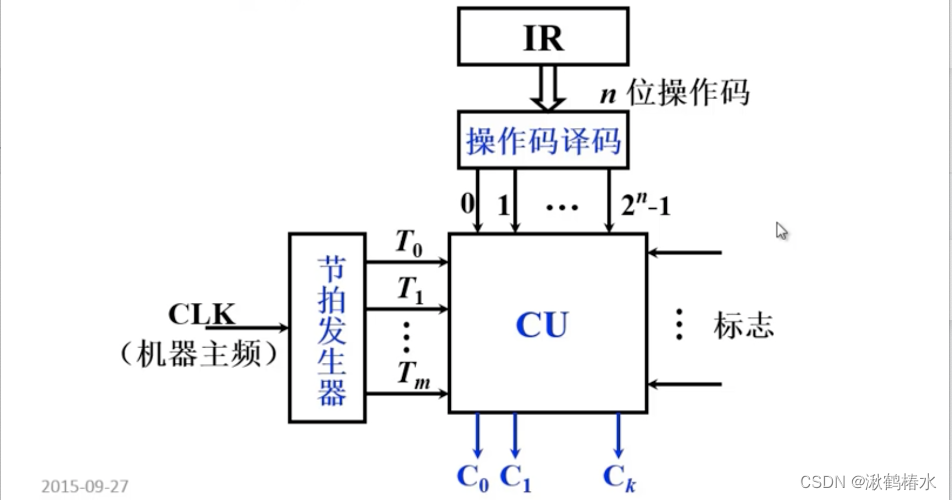

- CU外特性

- 机器主频通过节拍发生器产生不同的节拍信号,不同节拍信号对应某条指令的某个微操作的起始。

- 标志用来判断上条指令的结果是否满足该条跳转指令的跳转条件等

- IR中的操作码经过操作码译码器后,只有一条线为高电平1,就对应操作码的各种操作。

- 经过三方面的输入,每个节拍下,都会有一个控制信号输出(或者多个可以并行的控制信号同时发出)

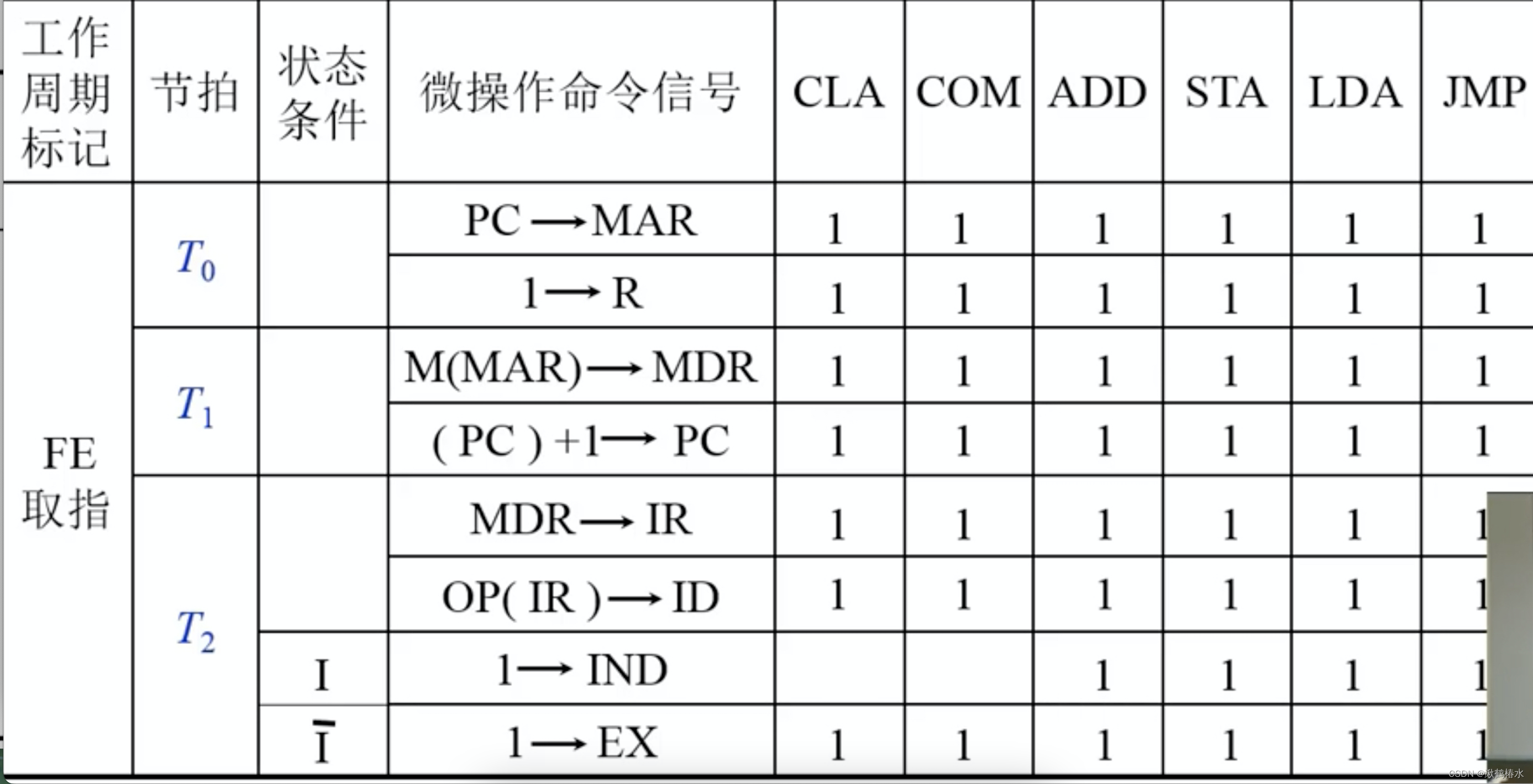

B、微操作的节拍安排(同步方式,一个机器周期有三个节拍)

上面C1到C12个控制指令、ALU右端的控制信号(控制ALU要作什么运算)、标志的修改(根据ALU的运算结果)、这些控制信号都在节拍的控制下由CU给出。

C、微操作安排的原则

- 微操作之间的顺序不能随意更改,例如指令必须在从内存中取出后,才能够将操作码送入CU译码。

- 互相关涉的部件不冲突,没有先后顺序(可以并行)的指令,尽量安排在一个时钟周期执行。

- 占用时间较短的微操作尽量安排在一个节拍中执行,微操作间允许有先后顺序。

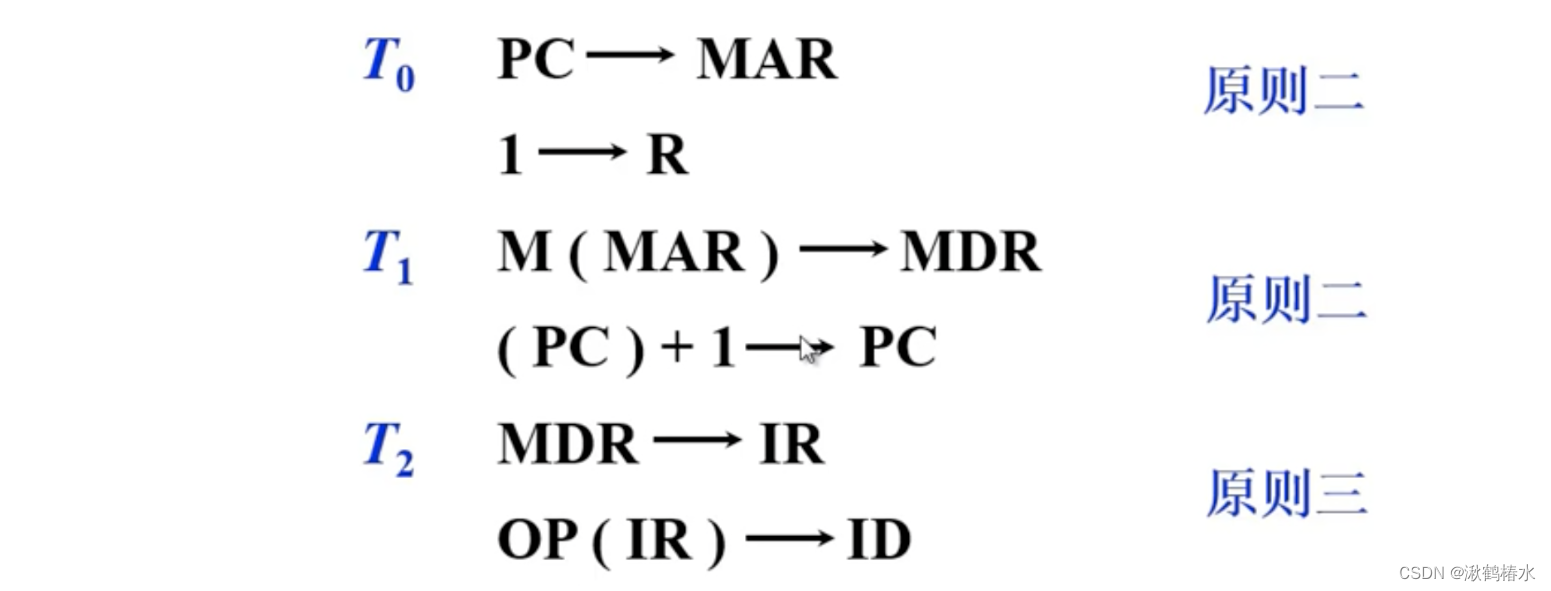

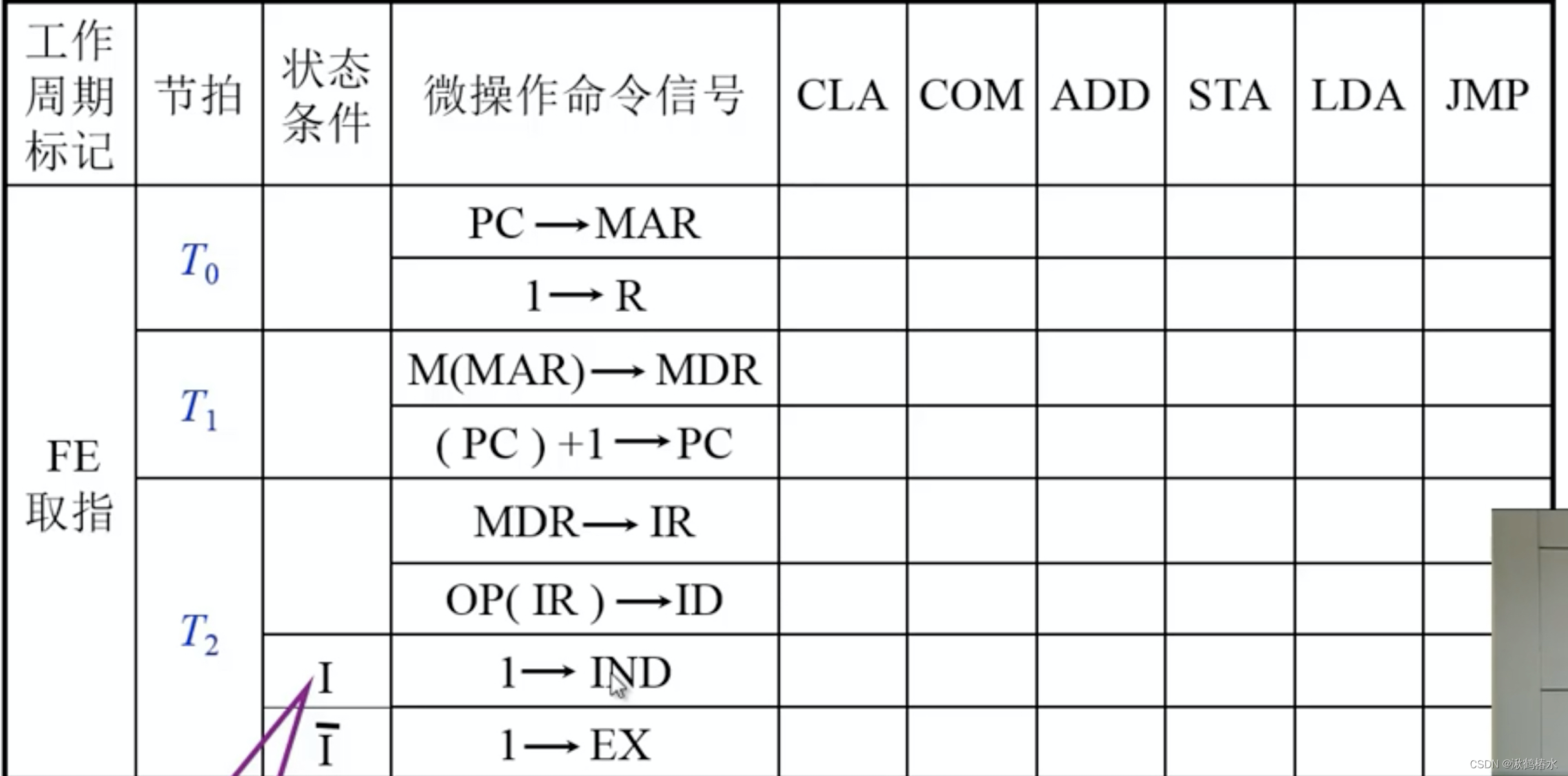

取指周期微操作的节拍安排

- 第一个节拍,PC中的指令地址送入MAR中;CU向主存发出读指令。(按照原则二,这两个指令关涉的部件不一样,可以并行)

- 第二个节拍,主存根据地址,将指令返回MDR;PC中的地址+1;(原则二)

- 第三个节拍,MDR中的指令送入IR寄存器;指令中的操作码被送入到ID(指令解析器)当中。

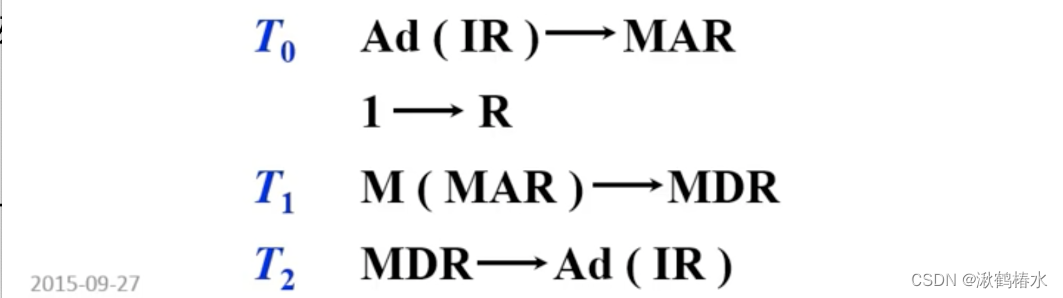

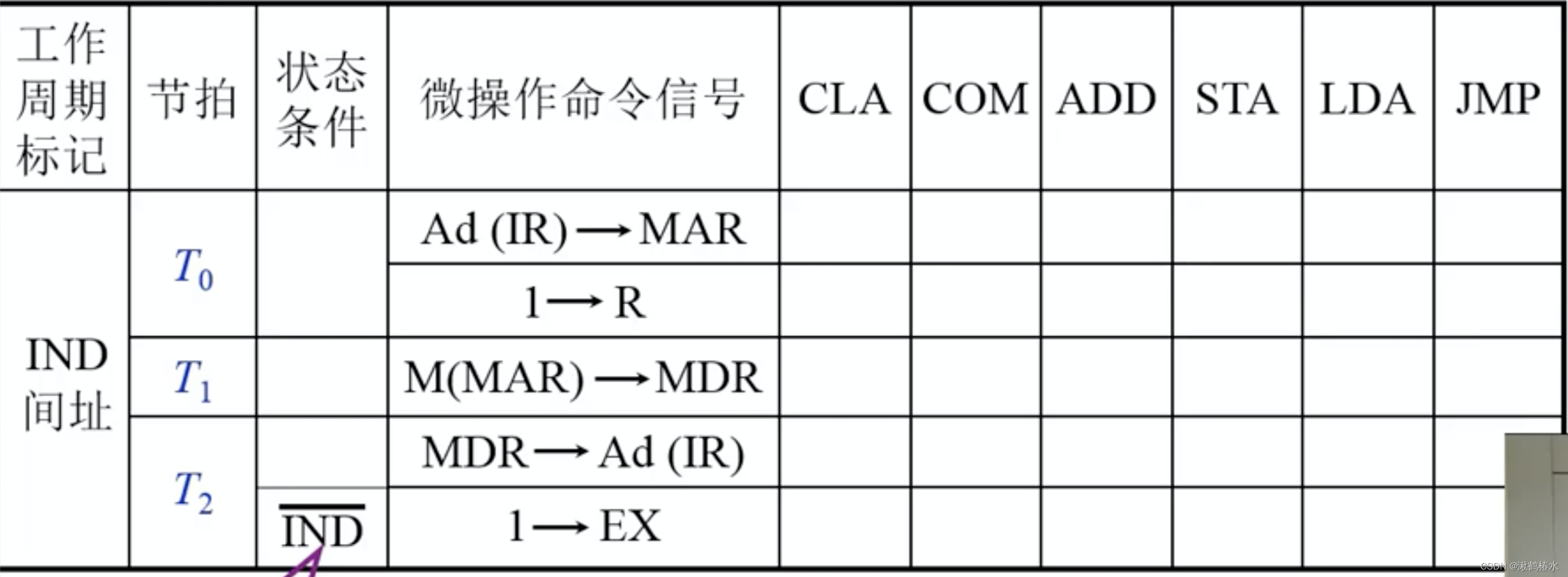

间址周期微操作的节拍安排

- 第一节拍,IR中的形式地址送入MAR中;同时,CU向存储单元发送读指令。

- 第二节拍,存储器中的真实地址被送入MDR中。

- 第三节拍,MDR中的真实地址同步到IR中指令的地址码部分,方便下步执行周期获取操作数。

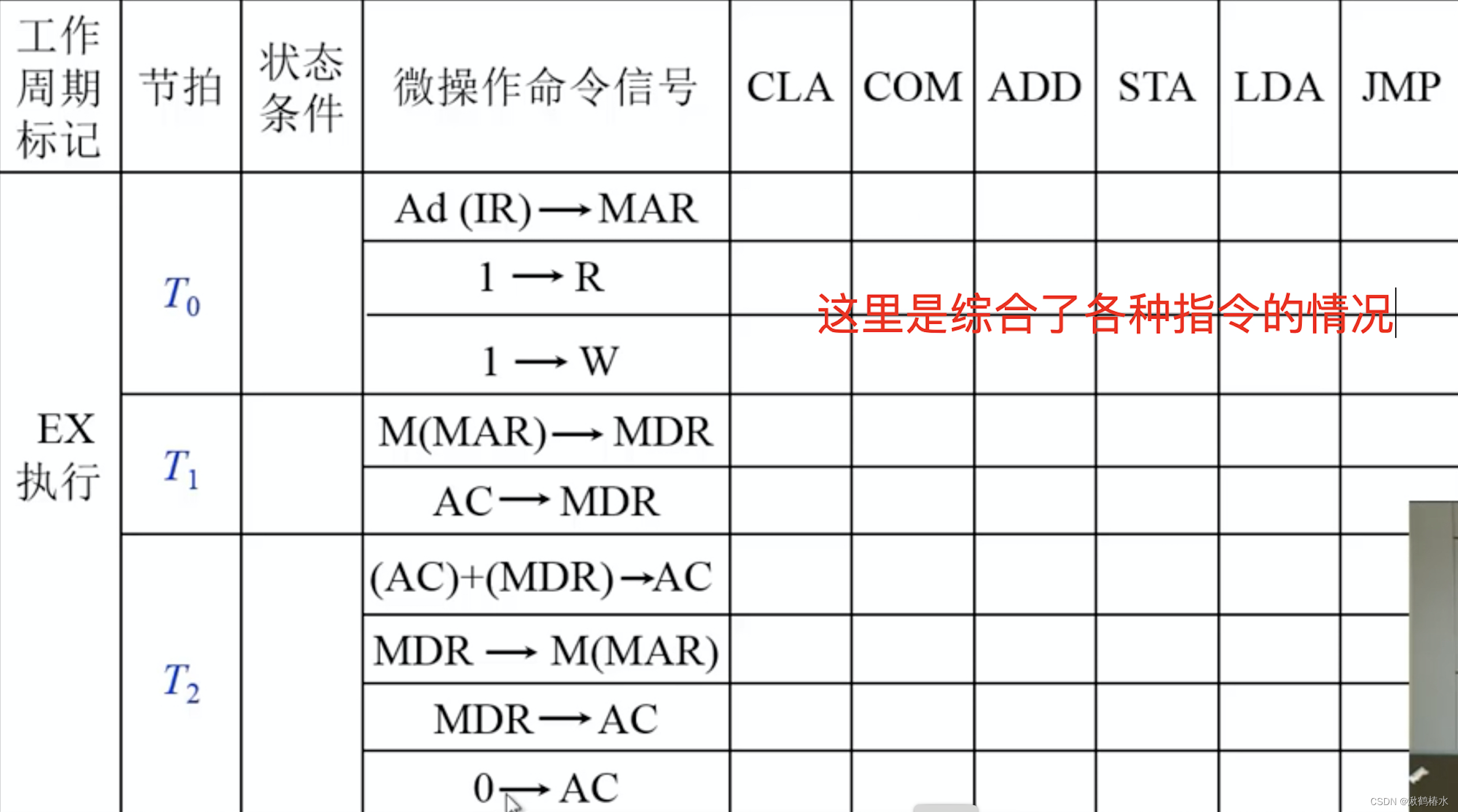

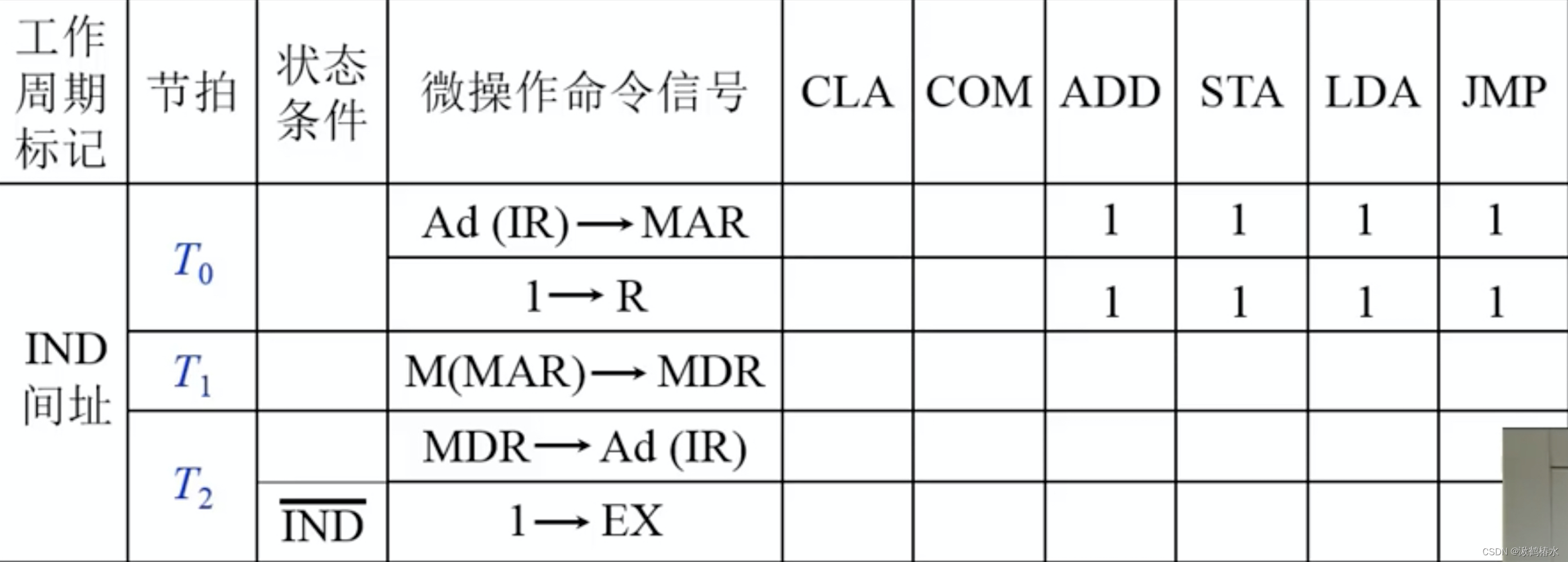

执行周期微操作的节拍安排(不同指令,安排不同)

T0 无、 T1 无、

T2 L(AC)-> R(AC) 右移操作

AC0 -> AC0 (保持符号位操作)

CSL(循环位移)T0 无、 T1 无、

T2 R(AC)-> L(AC)

AC0 -> ACn

STP(停机指令)T0 无、 T1 无、

T2 0 -> G(停机触发器)

ADD X (加数指令)

T0 Ad(IR) -> MAR 1 -> R

T1 M(MAR)存储器对应内容 -> MDR

T2 AC和MDR中两个操作数相加。各种打开控制门操作等

STA X (将数据写入存储器)T0 Ad(IR)-> MAR 1 -> w(读指令)

T1 AC(要存入的数据) -> MDR

T2 MDR -> M(内存)

LDA X (将数据读出存储器)T0 Ad(IR)-> MAR 1 -> R(读指令)

T1 M存储器对应单元-> MDR

T2 MDR -> ACC

JMP X (无条件跳转指令)T0 无、 T1 无、

T2 Ad(IR)-> PC

(将跳转的地址送入PC即可)

BAN X (条件分支指令)T0 无、 T1 无、

T2

( 根据条件判断将不同地址送入PC)

A0*Ad(IR) + 0 * PC -> PC

这里实际是根据标志生成器的结果送入不同地址到PC,标志生成器会根据ACC中结果不同给出不同标志送入CU。这里是简化了表达。

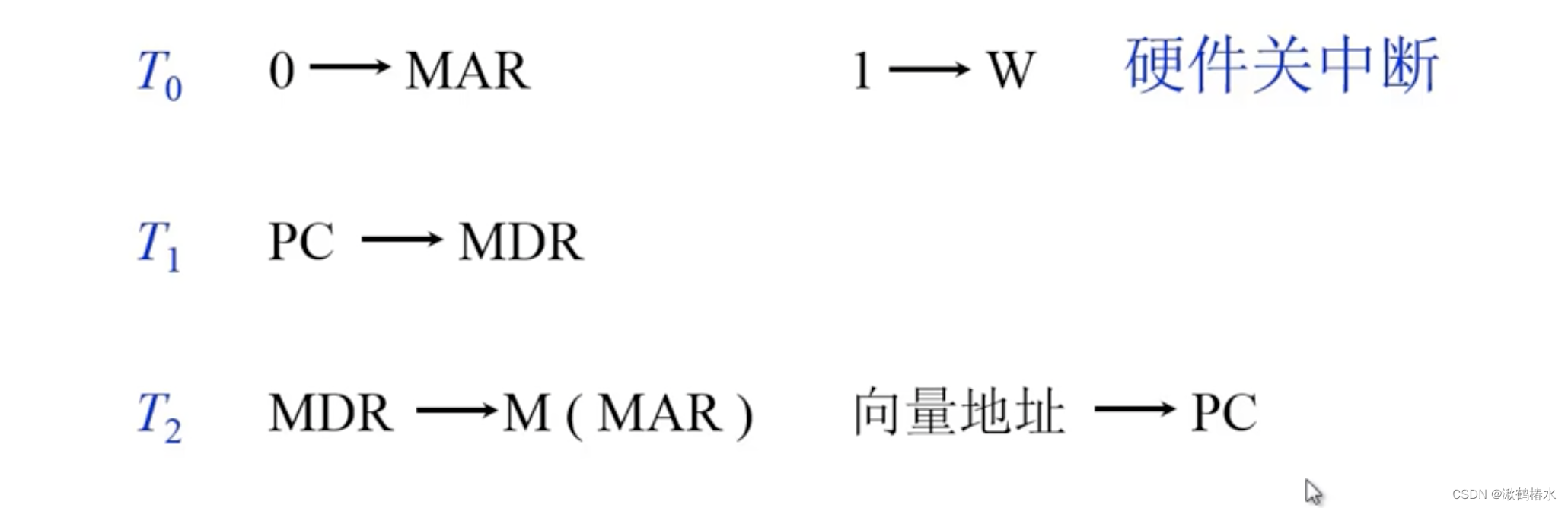

中断周期微指令的节拍安排

- 第一个节拍,将0地址送入MAR中;同时CU向主存发送写命令;

- 第二个节拍,将PC中要保存的断点送入MDR;

- 第三个节拍,MDR中断点存入存储器,同时向量地址生成中断程序首地址存入PC;

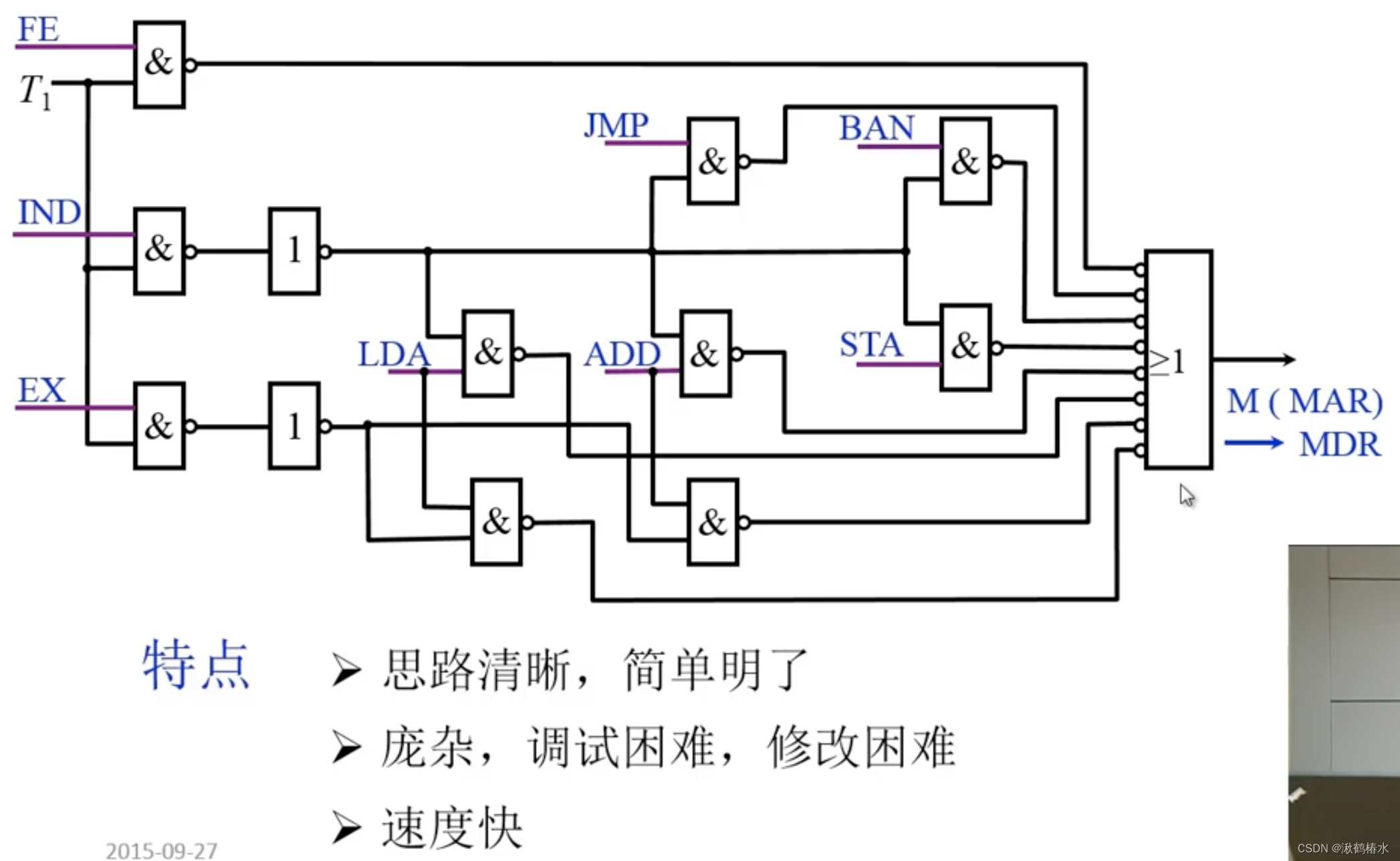

组合逻辑的设计步骤

- 列出时间表

状态标签是I,如果有多个状态标签,就可以进入多次间址周期。

- 每个指令可能有的阶段

硬件结构图及特点:

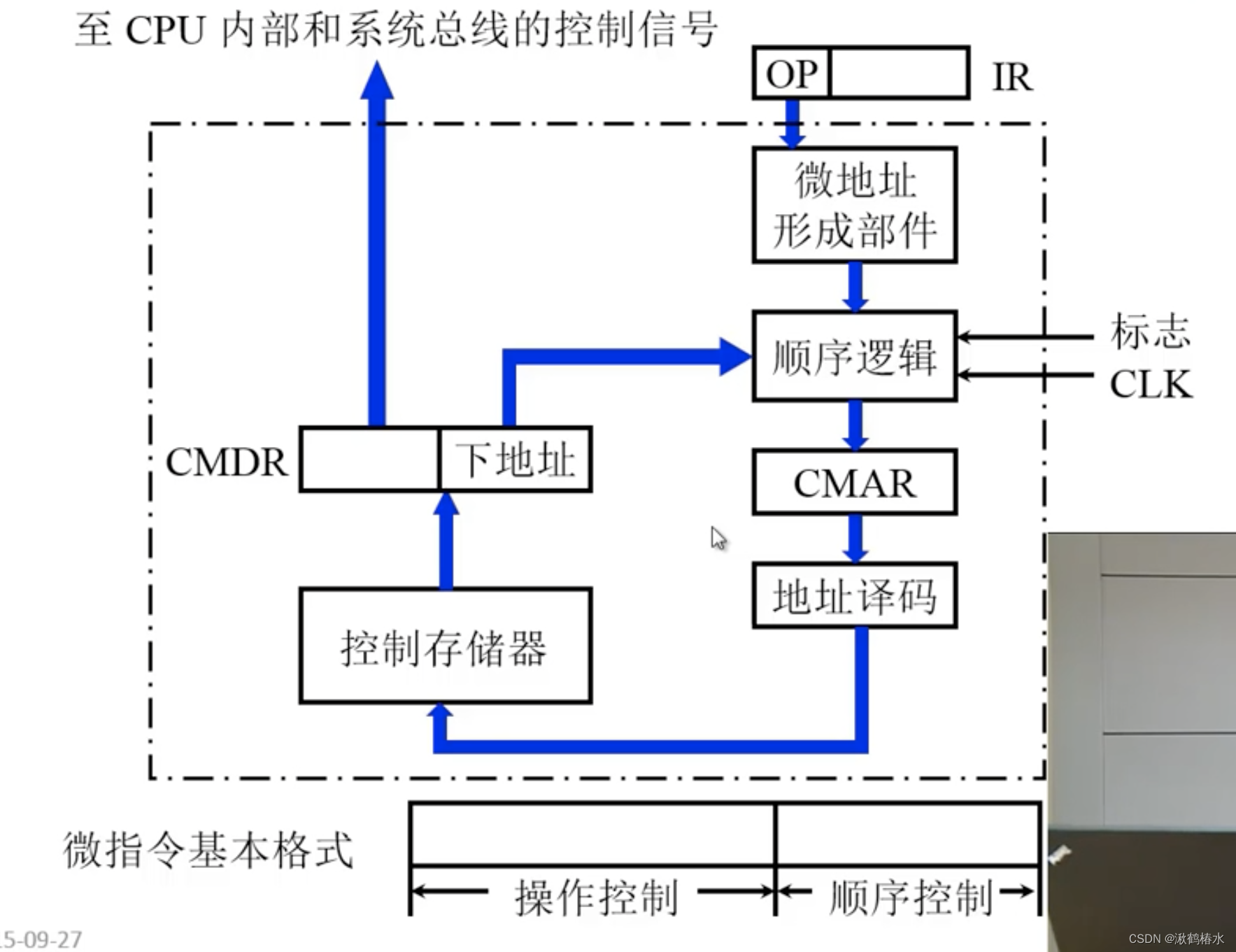

(六)微程序方式设计控制信号发送

大概就是上面的设计方式,把每个节拍需要用到的控制信号都存入控制储存器,当第一个指令要取出时,就要先将PC的值送入微地址形成部件,经顺序逻辑选择后放入MAR,从控制存储器取出微指令,微指令包含两部分一部分是控制信号,取出后会直接跟相关控制信号发送给对应部件,另一部分对应下一个微指令的地址。

注:计算机组成原理的笔记均根据哈工大mooc资源整理。

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"计算机组成原理(五)":http://eshow365.cn/6-30326-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: diffusers-Load adapters

- 下一篇: 前端工程师掌握技术