FPGA的通用FIFO设计verilog,1024*8bit仿真,源码和视频

最佳答案 问答题库518位专家为你答疑解惑

名称:FIFO存储器设计1024*8bit

软件:Quartus

语言:Verilog

本代码为FIFO通用代码,其他深度和位宽可简单修改以下参数得到

reg [7:0] ram [1023:0];//RAM。深度1024,宽度8

代码功能:

设计一个基于FPGA的FIFO存储器,使之能提供以下功能

1.存储空间至少1024 储器

2.存储位宽8bit

3.拓展功能:存储器空、满报警

演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=206

FPGA代码资源下载网:hdlcode.com

代码下载:

设计一个基于FPGA的FIFO存储器,使之能提供以下功能 1.存储空间至少1024 储器 2.存储位宽8bit 3.拓展功能:存储器空、满报警名称:FIFO存储器设计1024*8bit(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:设计一个基于FPGA的FIFO存储器,使之能提供以下功能 1.存储空间至少1024 储器 2.存储位宽8bit 3.拓展功能:存储器空、满报警演示视频:FPGA代码资源下载网:hdlcode.com部分代码展示//fifo 1024*8bit fifo//存储空间1024//位宽8bi![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=206

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=206

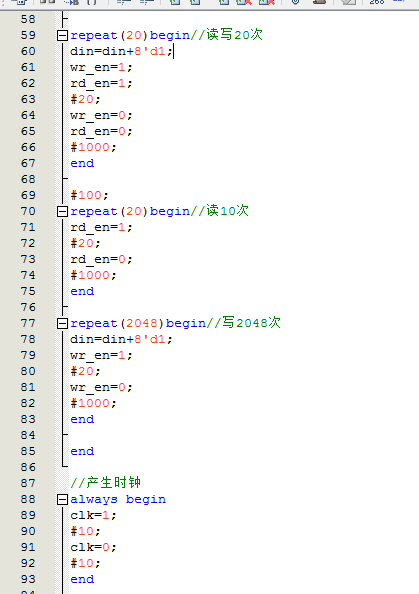

部分代码展示

//fifo 1024*8bit fifo

//存储空间1024

//位宽8bit

module a_fifo

(

input clk,//时钟

input rst,//复位

input [7:0] din,//fifo写数据

input wr_en,//写使能

input rd_en,//读使能

output reg [7:0] dout,//读数据

output empty,//空信号

output full//满信号

);

reg [7:0] ram [1023:0];//RAM。深度1024,宽度8

reg [11:0] count=12'd0;

reg [11:0] rp=12'd0;

reg [11:0] wp=12'd0;

integer i;

always@(posedge clk)

if(rst)begin//复位

wp<=12'd0;

rp<=12'd0;

dout<=8'd0;

count<=12'd0;

for(i=0;i<1024;i=i+1)

ram[i]<=8'b00000000;//清零

end

else

case({rd_en,wr_en})

2'b00:count<=count;

2'b01://单写FIFO

if(~full)begin//未满

ram[wp]<=din;//存入fifo

if(wp>=12'd1023)

wp<=12'd0;//写地址循环累加

else

wp<=wp+12'd1;

count<=count+12'd1;

rp<=rp;

end

2'b10://单读FIFO

if(~empty)begin//未空

dout<=ram[rp];//读fifo

if(rp>=12'd1023)

rp<=12'd0;//读地址循环累加

else

rp<=rp+12'd1;

count<=count-12'd1;

end

2'b11://同时读写FIFO

if(empty)begin//FIFO为空,只能写

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

3. 程序编译

4. Testebnch

5. 仿真图

仿真图依次仿真了如下功能:

具体功能1/2/3对应如下:

1:写FIFO 20次,再读20次,FIFO读空

1. 写FIFO 10次,然后同时读写20次,最后读10次,FIFO读空

2. 连续写FIFO 2048次,FIFO写满

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"FPGA的通用FIFO设计verilog,1024*8bit仿真,源码和视频":http://eshow365.cn/6-20503-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!