Systemverilog断言介绍(四)

最佳答案 问答题库638位专家为你答疑解惑

3.3 SEQUENCES, PROPERTIES, AND CONCURRENT ASSERTIONS

3.3.1 SEQUENCE SYNTAX AND EXAMPLES

一个序列是在一段时间内发生的一组值的规范。构建序列所使用的基本操作是延迟规范器,形式为##n(表示特定数量的时钟)或##[a:b](表示在a和b个时钟之间的可变延迟)。特殊符号$可用于序列的上界,指定可能无限数量的周期。当序列的指定值全部发生时,称该序列被匹配。具有可变延迟的序列在任何执行跟踪过程中可能有多个重叠的匹配。下图展示了一些简单的sequence例子:

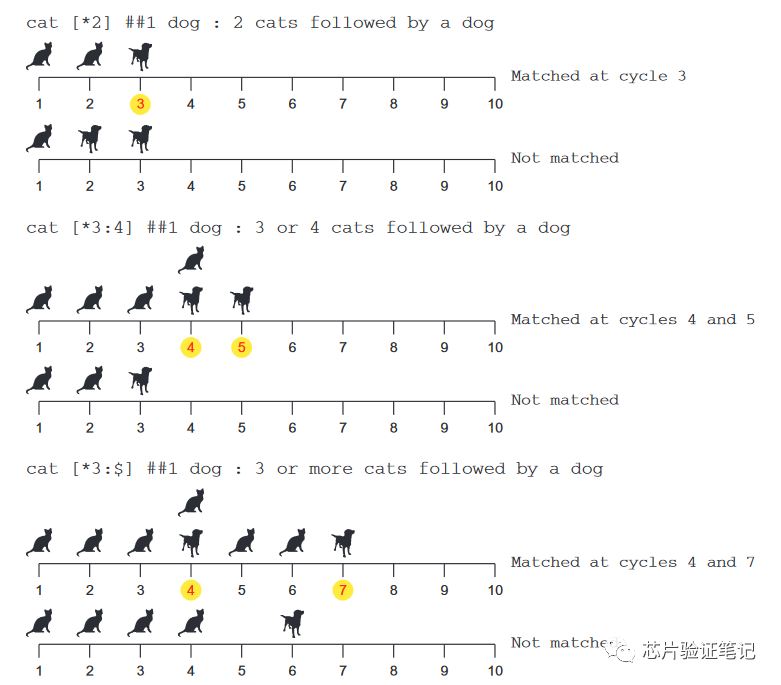

另一个常见的序列操作是重复运算符[m:n]。这表示一个子序列将被重复一定次数。同样,上界可以是$,表示可能会有无限次重复。下图展示了使用该运算符的一些示例:

序列可以使用and、or或者操作符进行逻辑组合。(注意,这些与SystemVerilog中提供的||和&&操作符是不同的,后者用于布尔表达式的逻辑与或运算。)使用and操作符时,表示两个序列同时开始,尽管它们的结束点可能不匹配。对于or操作符而言,两个序列中必须有一个匹配。此外,throughout操作符非常有用,它检查某个布尔表达式在整个序列的执行过程中始终为真;within操作符也很有用,它检查一个序列是否发生在另一个序列的执行过程中。下图展示了使用这些操作符的一些示例:

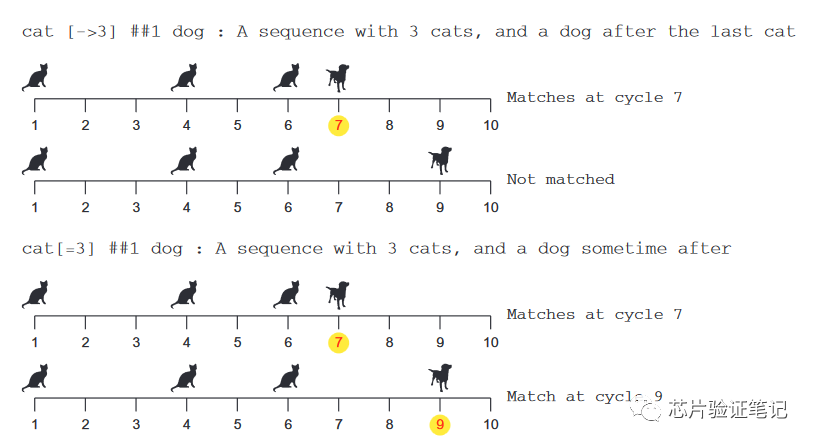

通常有用的最后一组序列操作符是跳转重复操作符[- > n]和[ = n]。它们表示某个值在序列中恰好出现n次,尽管这些出现可能是不连续的,并且在它们之间可能有任意其他活动。简单的跳转[- > n]在该值的最后一次出现时匹配,而非连续的跳转[ = n]允许在最后一次出现之后有任意的其他活动。下图显示了一些示例:

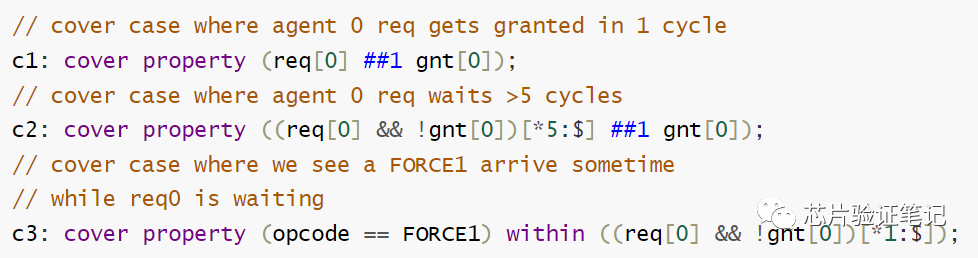

除非作为断言语句的一部分,否则序列是没有用的;上面的简单示例在技术上是代码片段,而不是有用的语句。将序列作为断言或假设是没有意义的,但序列在构建覆盖属性方面非常有用。下面是一些可能在仲裁器示例中有用的覆盖断言语句的示例:

转自:芯片验证笔记

99%的人还看了

相似问题

- 【Django-DRF用法】多年积累md笔记,第3篇:Django-DRF的序列化和反序列化详解

- 【Java 进阶篇】JavaScript JSON 语法入门:轻松理解数据的序列化和反序列化

- 【python学习】基础篇-常用模块-pickle模块:序列化和反序列化

- ZC序列理论学习及仿真

- 时间序列预测实战(十七)PyTorch实现LSTM-GRU模型长期预测并可视化结果(附代码+数据集+详细讲解)

- 代码随想录算法训练营第二十九天| 491 递增子序列 46 全排列

- 最长递增子序列

- 深入解析序列模型:全面阐释 RNN、LSTM 与 Seq2Seq 的秘密

- c#Nettonsoft.net库常用的方法json序列化反序列化

- 基于C#实现最长公共子序列

猜你感兴趣

版权申明

本文"Systemverilog断言介绍(四)":http://eshow365.cn/6-20004-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: LuaJIT编写的解析十六进制数据

- 下一篇: Linux程序调试器——gdb的使用