已解决

DDS信号发生器Verilog波形发生器FPGA

来自网友在路上 184884提问 提问时间:2023-10-02 04:29:01阅读次数: 84

最佳答案 问答题库848位专家为你答疑解惑

名称:DDS信号发生器Verilog波形发生器

软件:Quartus

语言:Verilog

要求:

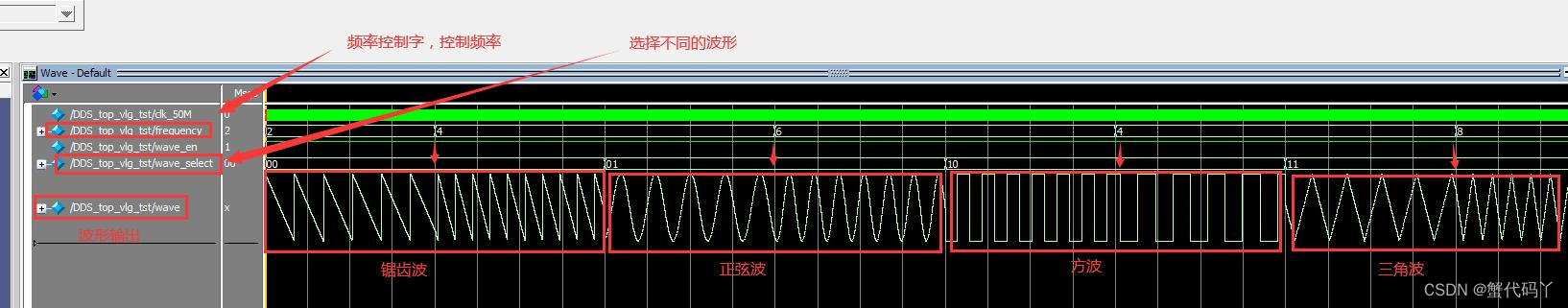

1.可产生正弦波,锯齿波,三角波,方波4种波形,频率可调

2.具有波形选择、起动、停止功能。

代码下载:DDS信号发生器Verilog波形发生器_Verilog/VHDL资源下载

代码网:hdlcode.com

![]()

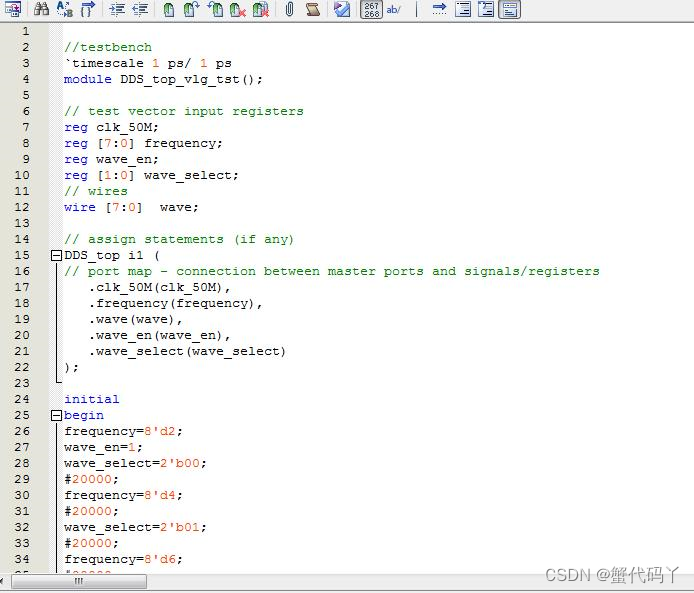

部分代码展示

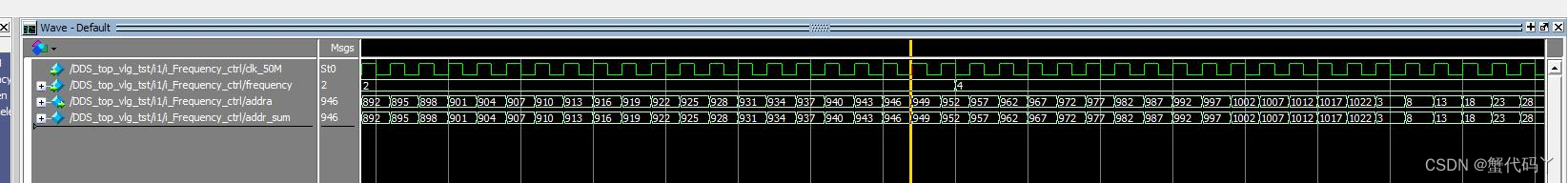

`timescale 1ns / 1ps //输出频率f=clk_50M*frequency/2^10 module DDS_top(input clk_50M,//时钟输入input wave_en,//波形起的停止开关input [1:0] wave_select,//波形选择开关:00输出锯齿波,01输出sin,10输出方波,11输出三角波input [7:0] frequency,//频率控制字,控制输出波形频率output [7:0] wave//输出波形);wire [9:0] addra; wire [7:0] douta_fangbo; wire [7:0] douta_sanjiao; wire [7:0] douta_sin; wire [7:0] douta_juchi; //锯齿ROM juchi_ROM i_juchi_ROM (.clock(clk_50M), // input wire clka.address(addra), // input wire [9 : 0] addra.q(douta_juchi) // output wire [7 : 0] douta); //方波ROM fangbo_ROM i_fangbo_ROM (.clock(clk_50M), // input wire clka.address(addra), // input wire [9 : 0] addra.q(douta_fangbo) // output wire [7 : 0] douta);//三角波ROM sanjiao_ROM i_sanjiao_ROM (.clock(clk_50M), // input wire clka.address(addra), // input wire [9 : 0] addra.q(douta_sanjiao) // output wire [7 : 0] douta ); //sin波ROM sin_ROM i_sin_ROM (.clock(clk_50M), // input wire clka.address(addra), // input wire [9 : 0] addra.q(douta_sin) // output wire [7 : 0] douta ); //相位累加器 Frequency_ctrl i_Frequency_ctrl( . clk_50M(clk_50M), . frequency(frequency),//频率控制字 . addra(addra)//输出地址); //波形选择控制 wave_sel i_wave_sel( . clk_50M(clk_50M), . wave_en(wave_en), . wave_select(wave_select),//00输出锯齿波,01输出sin,10输出方波,11输出三角波 . douta_fangbo(douta_fangbo),//方波 . douta_sanjiao(douta_sanjiao),//三角 . douta_sin(douta_sin), //正弦 . douta_juchi(douta_juchi), . wave(wave)//输出波形 ); endmodule

设计文档(文档点击可下载):

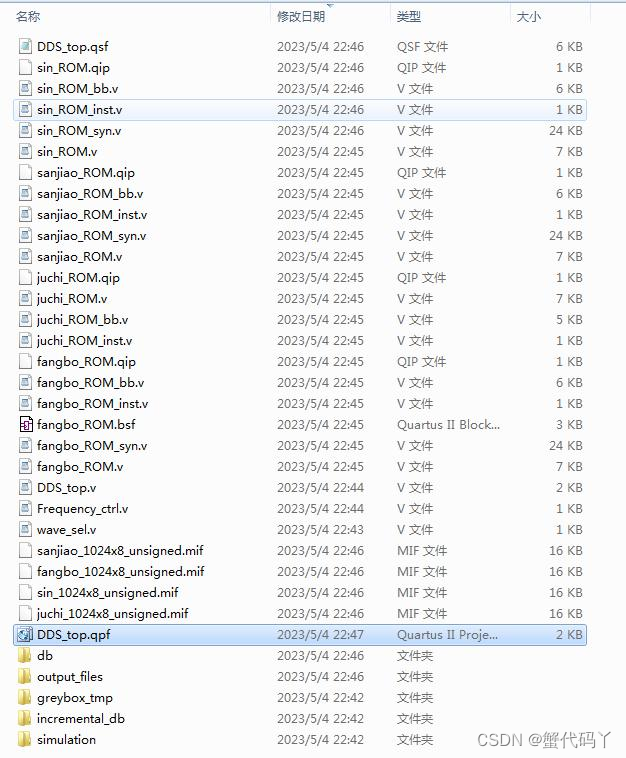

1. 工程文件

2. 程序文件

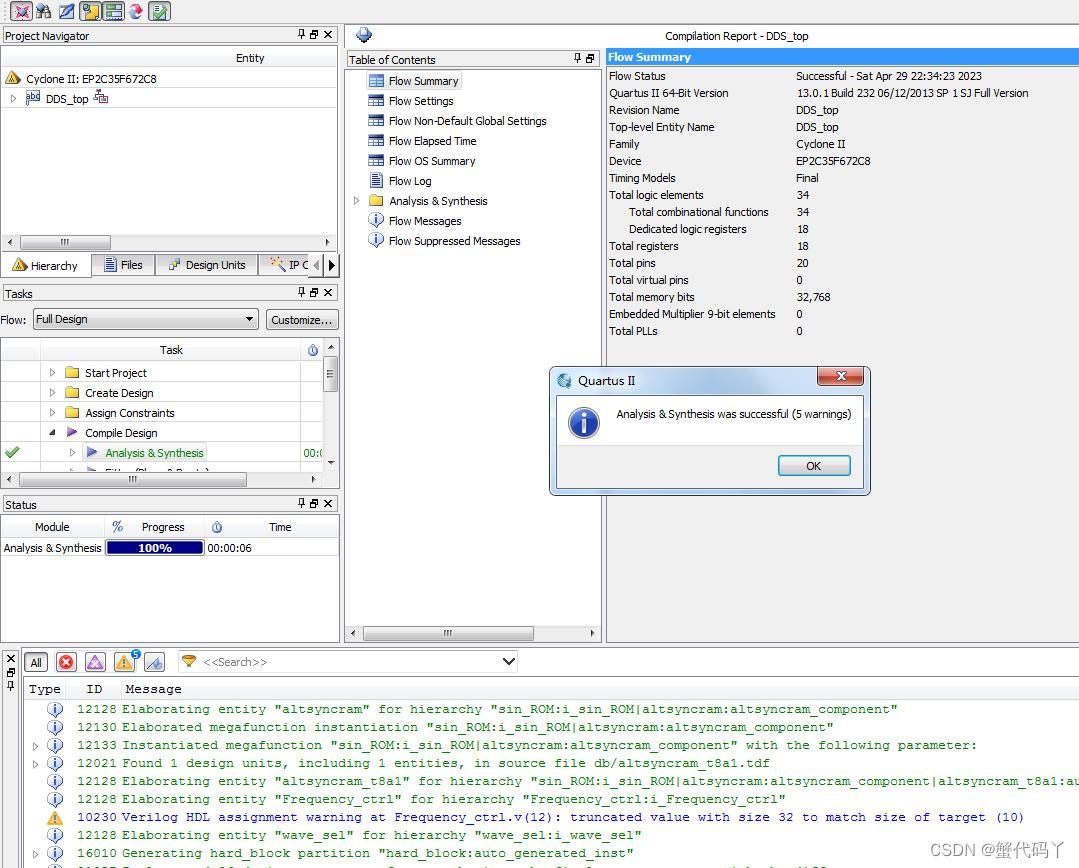

3. 程序编译

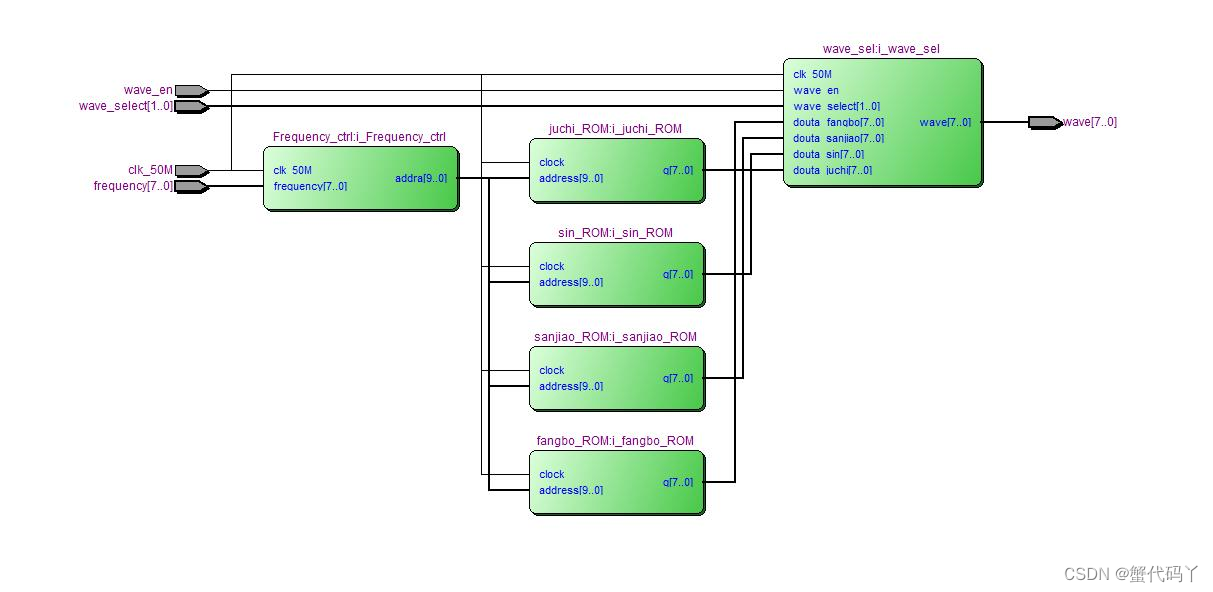

4. RTL 图

5. Testbench

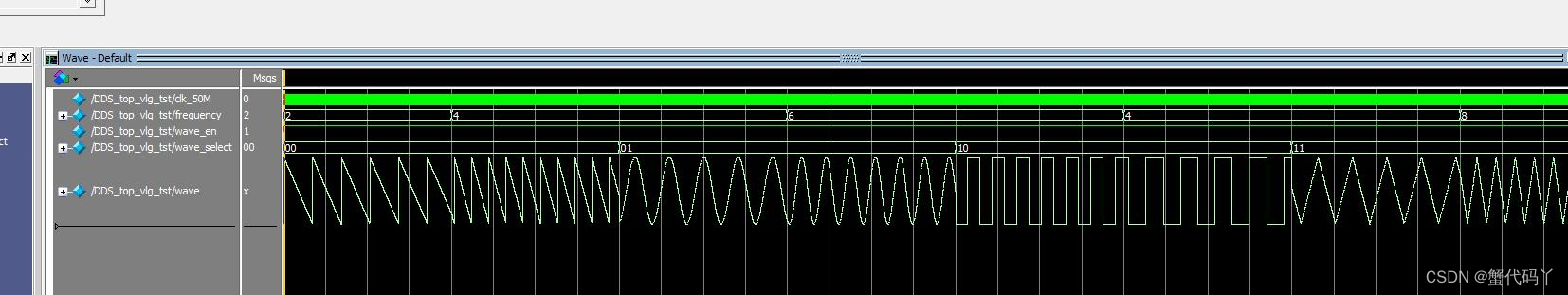

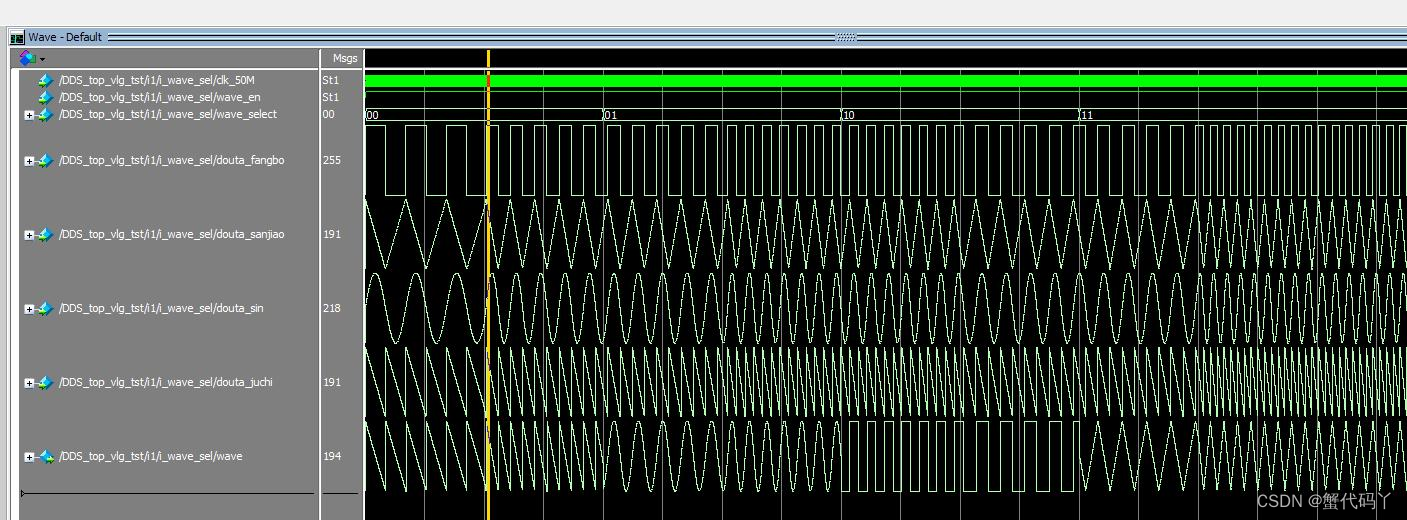

6. 仿真图

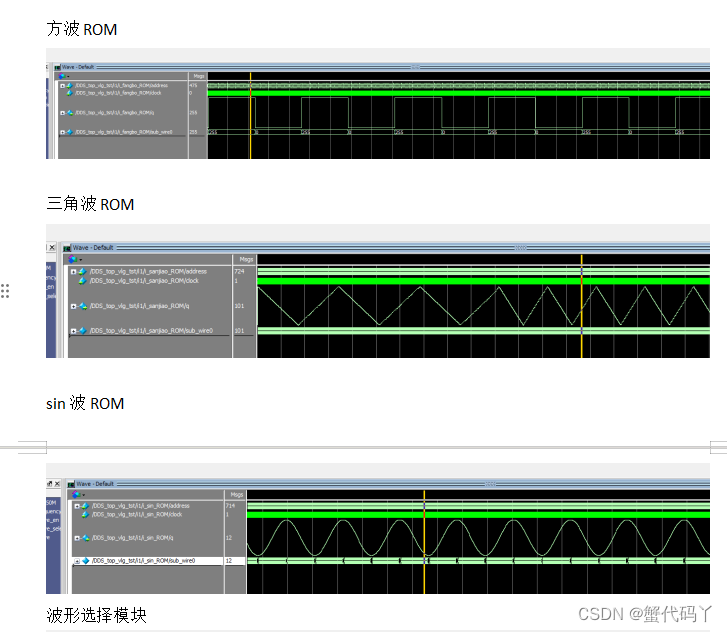

整体仿真图

相位累加器模块

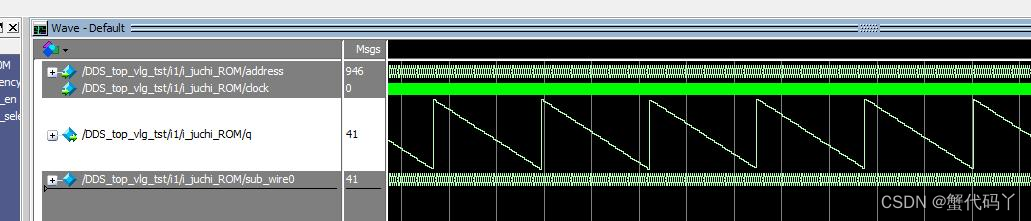

锯齿波 ROM

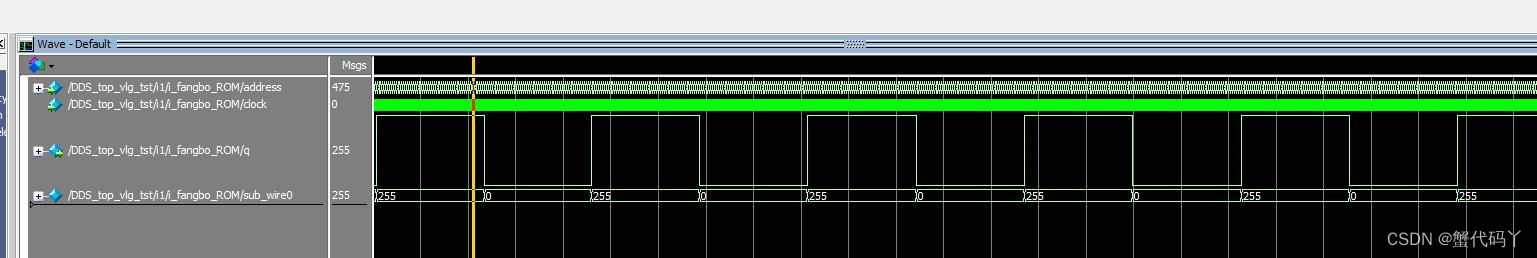

方波 ROM

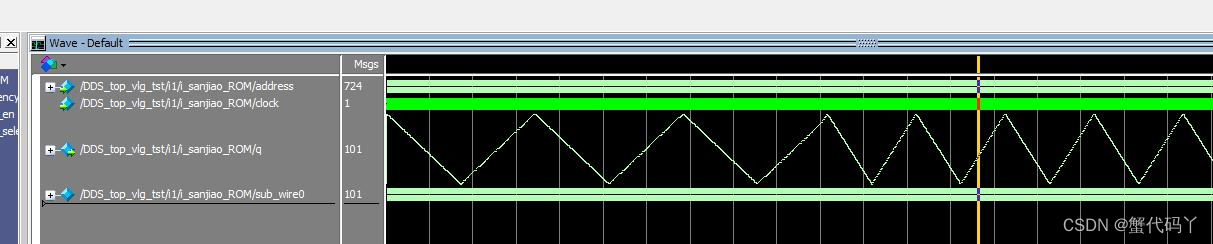

三角波 ROM

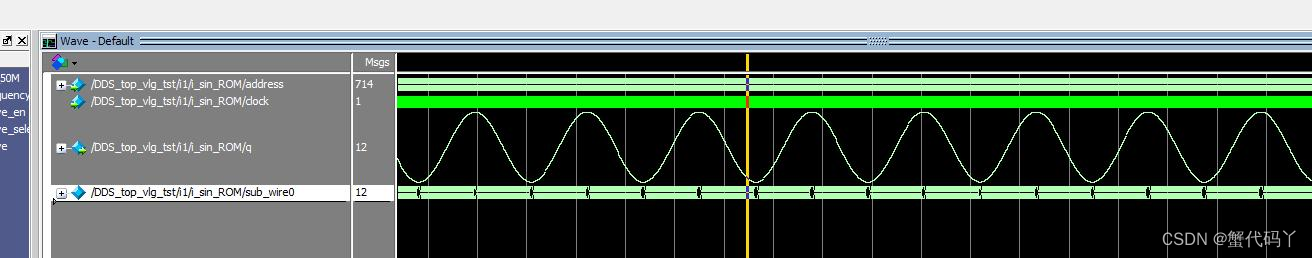

sin 波 ROM

波形选择模块

设计文档.doc

查看全文

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"DDS信号发生器Verilog波形发生器FPGA":http://eshow365.cn/6-15688-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!