已解决

【Verilog语法】比较不同计数器的运算方式,其中有一个数是延迟打一拍的效果,目的是使得两个计数器的结果相同。

来自网友在路上 182882提问 提问时间:2023-09-24 06:19:46阅读次数: 82

最佳答案 问答题库828位专家为你答疑解惑

比较不同计数器的运算方式,其中有一个数是延迟打一拍的效果,目的是使得两个计数器的结果相同。

- 1,第一种

- 2,第二种

- 3,第三种

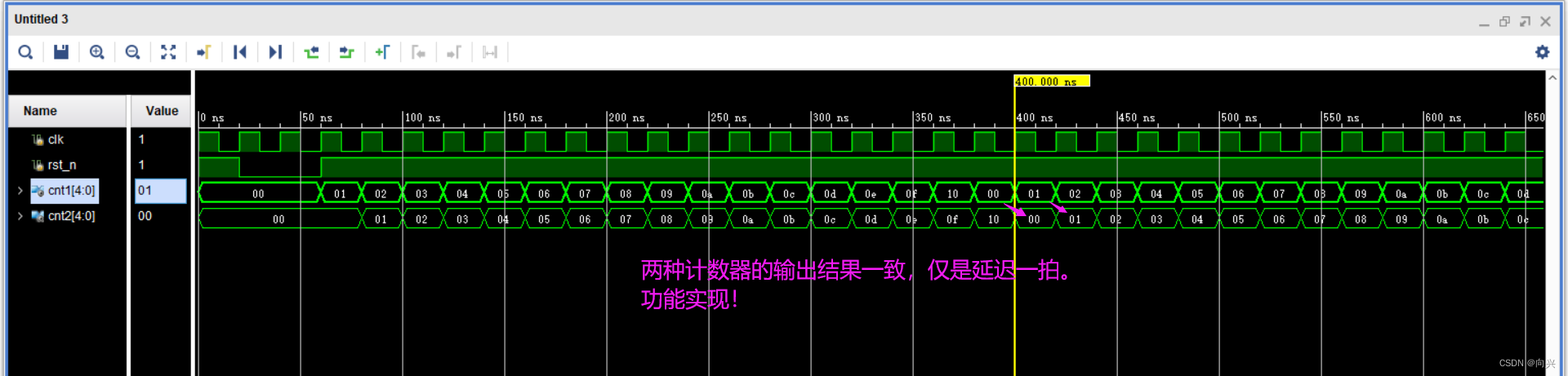

第三种方案,完成实现。

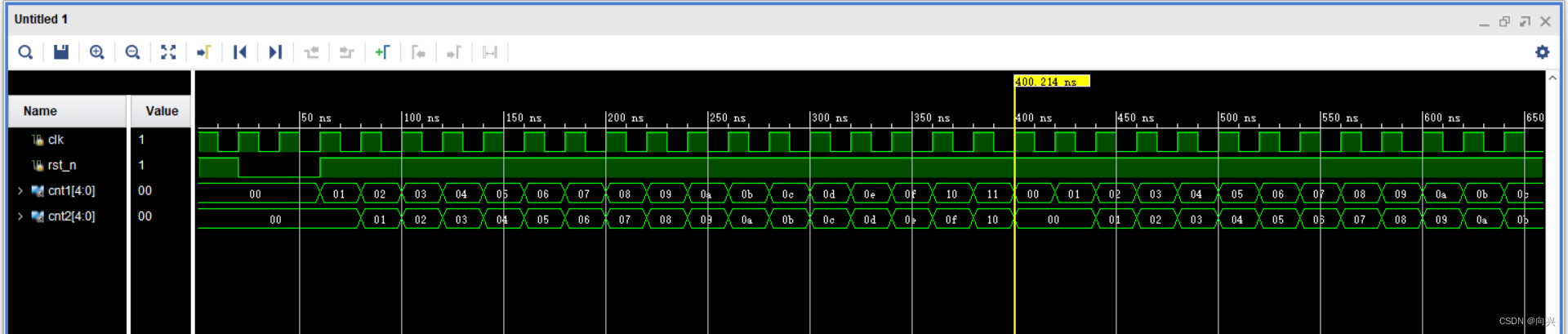

1,第一种

(1)RTL

module c(

input clk,

input rst_n,

// input a,

// input b,

output cnt1,

output cnt2

);reg [4:0] cnt1, cnt2;

always@(posedge clk or negedge rst_n) beginif(!rst_n) begincnt1 <= 0;cnt2 <= 0;endelse if(cnt1 <= 16) begincnt1 <= cnt1 + 1;cnt2 <= cnt1; endelse begincnt1 <= 0;cnt2 <= 0;end

endendmodule(2)TB

module tb_c;

reg clk;

reg rst_n;

wire [4:0] cnt1;

wire [4:0] cnt2;always #10 clk = ~clk;initial beginclk = 1; rst_n =1;#20; rst_n = 0;#40; rst_n = 1; end c uu(

.clk(clk),

.rst_n(rst_n),

.cnt1(cnt1),

.cnt2(cnt2)

);endmodule(3)仿真

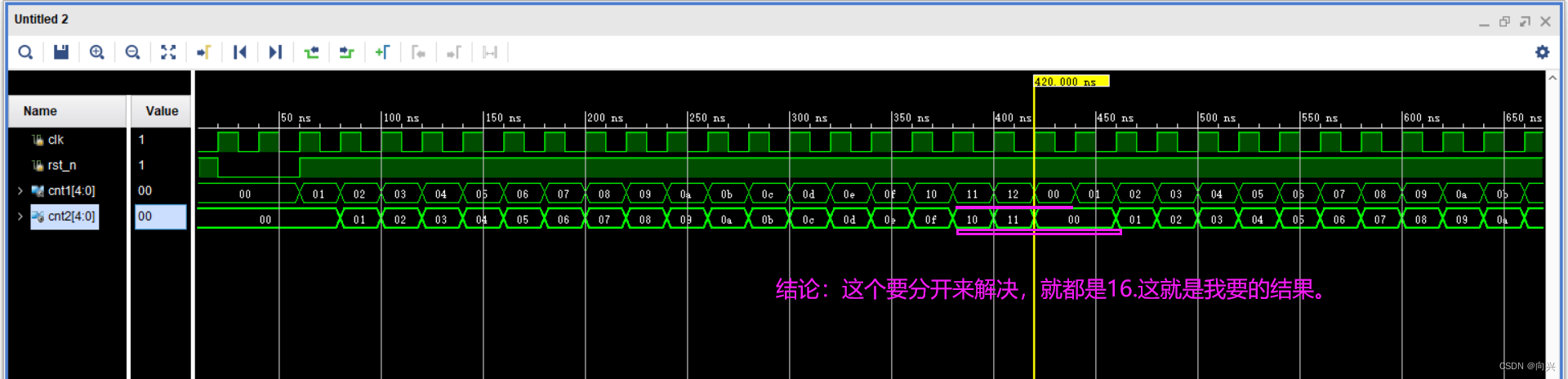

2,第二种

(1)RTL

module c(

input clk,

input rst_n,

// input a,

// input b,

output cnt1,

output cnt2

);reg [4:0] cnt1, cnt2;

always@(posedge clk or negedge rst_n) beginif(!rst_n) begincnt1 <= 0;cnt2 <= 0;endelse if(cnt2 <= 16) begincnt1 <= cnt1 + 1;cnt2 <= cnt1; endelse begincnt1 <= 0;cnt2 <= 0;end

endendmodule(2)TB

module tb_c;

reg clk;

reg rst_n;

wire [4:0] cnt1;

wire [4:0] cnt2;always #10 clk = ~clk;initial beginclk = 1; rst_n =1;#20; rst_n = 0;#40; rst_n = 1; end c uu(

.clk(clk),

.rst_n(rst_n),

.cnt1(cnt1),

.cnt2(cnt2)

);endmodule(3)仿真

3,第三种

(1)RTL

module c(

input clk,

input rst_n,

// input a,

// input b,

output cnt1,

output cnt2

);reg [4:0] cnt1, cnt2;

// 1

always@(posedge clk or negedge rst_n) beginif(!rst_n) begincnt1 <= 0;endelse if(cnt1 < 16) begincnt1 <= cnt1 + 1; // 1endelse begincnt1 <= 0;end

end// 2

always@(posedge clk or negedge rst_n) beginif(!rst_n) begincnt2 <= 0;endelse if(cnt2 < 16) begincnt2 <= cnt1; // 0endelse begincnt2 <= 0;end

endendmodule(2)TB

module tb_c;

reg clk;

reg rst_n;

wire [4:0] cnt1;

wire [4:0] cnt2;always #10 clk = ~clk;initial beginclk = 1; rst_n =1;#20; rst_n = 0;#40; rst_n = 1; end c uu(

.clk(clk),

.rst_n(rst_n),

.cnt1(cnt1),

.cnt2(cnt2)

);endmodule(3)仿真

查看全文

99%的人还看了

猜你感兴趣

版权申明

本文"【Verilog语法】比较不同计数器的运算方式,其中有一个数是延迟打一拍的效果,目的是使得两个计数器的结果相同。":http://eshow365.cn/6-12584-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: 用go实现cors中间件

- 下一篇: 使用python处理MNIST数据集