已解决

verilog学习笔记(1)module实例化2

来自网友在路上 177877提问 提问时间:2023-09-21 15:17:52阅读次数: 77

最佳答案 问答题库778位专家为你答疑解惑

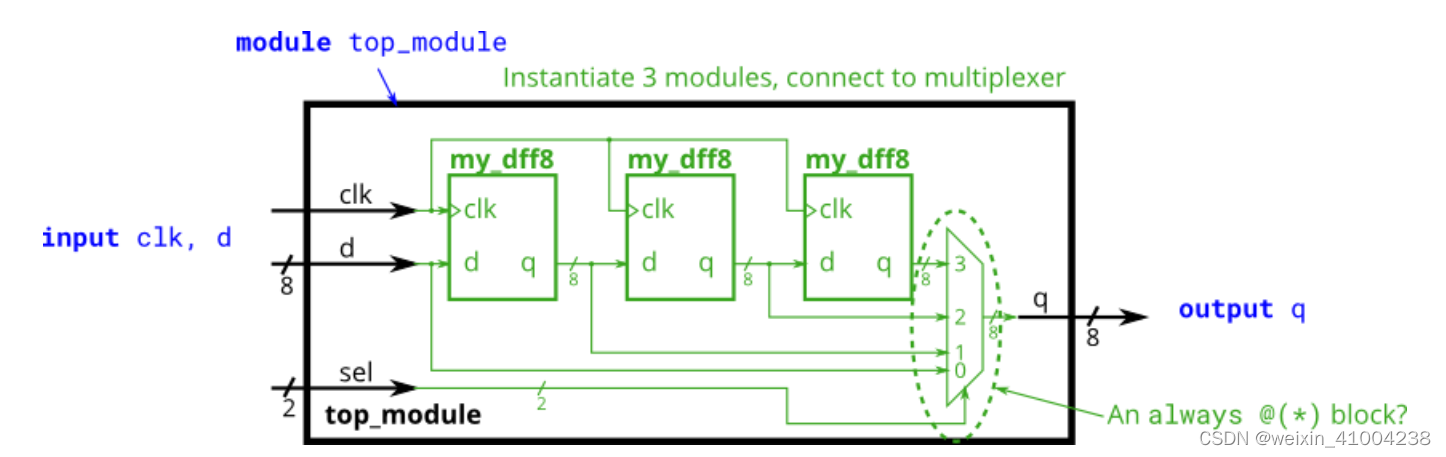

移位寄存器+多路选择器

我的代码:

module top_module ( input clk, input [7:0] d, input [1:0] sel, output [7:0] q

);wire [7:0] w1;wire [7:0] w2;wire [7:0] w3;my_dff8 my_dff8_1(.clk(clk),.d(d),.q(w1));my_dff8 my_dff8_2(.clk(clk),.d(w1),.q(w2));my_dff8 my_dff8_3(.clk(clk),.d(w2),.q(w3));always@(d or w1 or w2 or w3 or sel)beginif(sel == 2'b00 )q <= d;else if(sel == 2'b01 )q <= w1;else if(sel == 2'b10 )q <= w2;elseq <= w3;endendmodule答案:

module top_module (input clk,input [7:0] d,input [1:0] sel,output reg [7:0] q

);wire [7:0] o1, o2, o3; // output of each my_dff8// Instantiate three my_dff8smy_dff8 d1 ( clk, d, o1 );my_dff8 d2 ( clk, o1, o2 );my_dff8 d3 ( clk, o2, o3 );// This is one way to make a 4-to-1 multiplexeralways @(*) // Combinational always blockcase(sel)2'h0: q = d;2'h1: q = o1;2'h2: q = o2;2'h3: q = o3;endcaseendmodule查看全文

99%的人还看了

相似问题

猜你感兴趣

版权申明

本文"verilog学习笔记(1)module实例化2":http://eshow365.cn/6-10771-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!

- 上一篇: MyBatis 分页插件 PageHelper

- 下一篇: 收款码的费率都是多少