已解决

FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

来自网友在路上 160860提问 提问时间:2023-09-21 13:27:55阅读次数: 60

最佳答案 问答题库608位专家为你答疑解惑

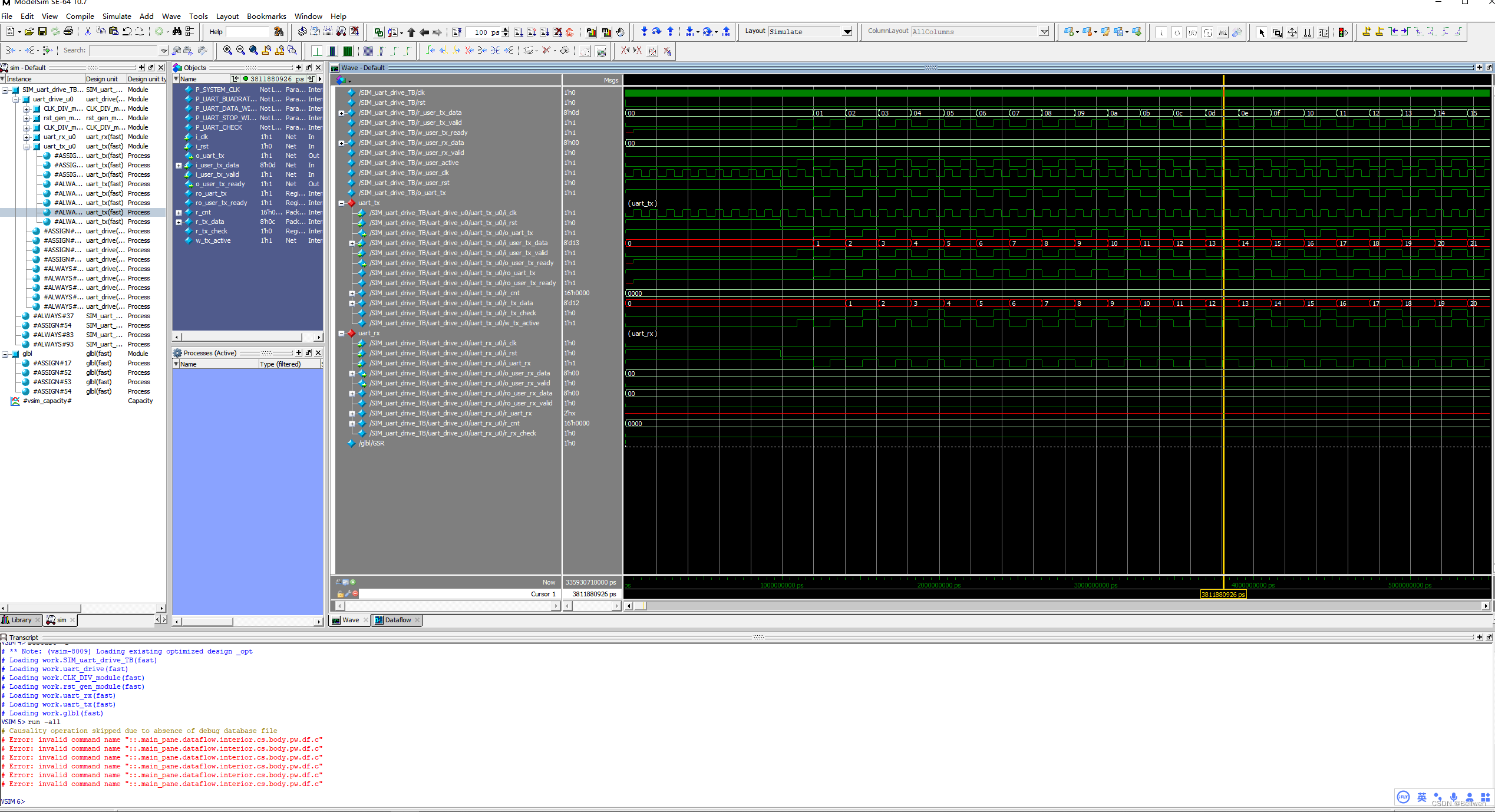

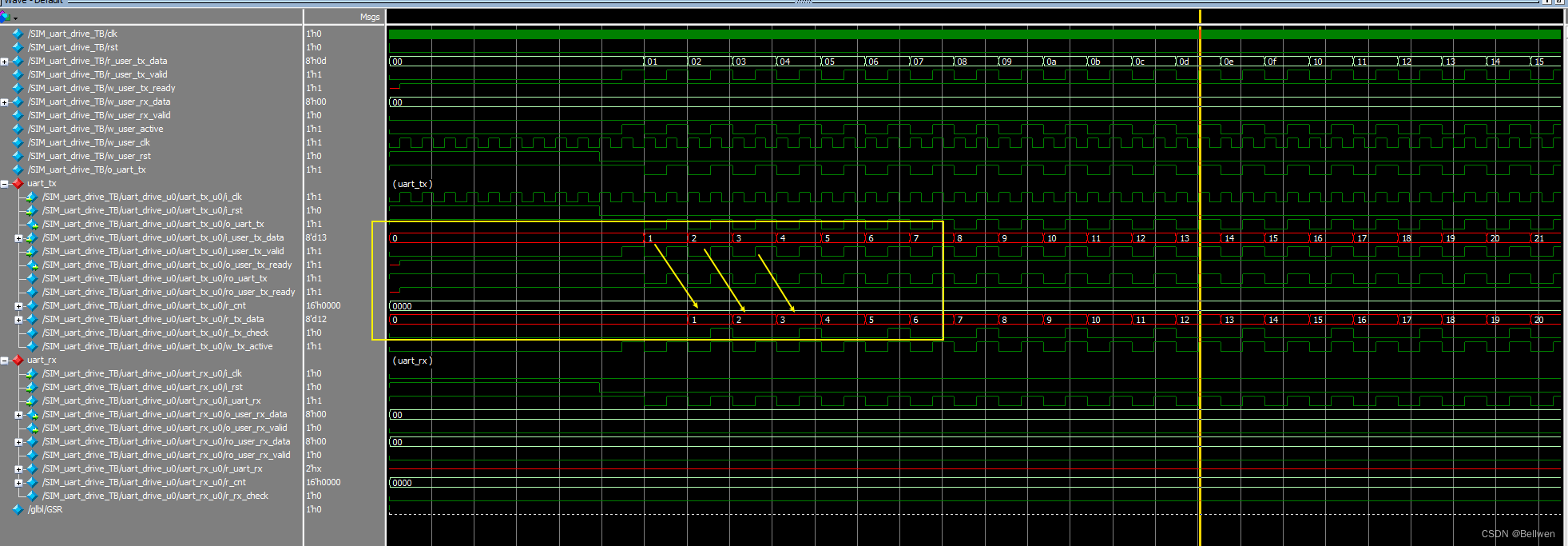

FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

仿真模块SIM_uart_drive_TB,仿真实现。

vivado联合modelsim进行仿真。

文章目录

- FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB

- 一、SIM_uart_drive_TB仿真代码

- 二、仿真结果

- 总结

一、SIM_uart_drive_TB仿真代码

`timescale 1ns / 1ns //时间单位/时间精度

//

// Company:

// Engineer:

//

// Create Date: 2023/09/12 14:52:47

// Design Name:

// Module Name: SIM_uart_drive_TB

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module SIM_uart_drive_TB();/****仿真语法、产生时钟与复位****/localparam CLK_PERIOD = 20 ;reg clk,rst;initial begin //过程语句,只在仿真里可以使用,不可综合rst = 1; //上电开始复位#100; //延时100ns@(posedge clk) rst = 0; //上电复位释放

endalways begin//过程语句,只在仿真里可以使用,不可综合clk = 0;#(CLK_PERIOD/2);clk = 1;#(CLK_PERIOD/2);

endlocalparam P_USER_DATA_WIDTH = 8;reg [P_USER_DATA_WIDTH - 1 : 0] r_user_tx_data ;

reg r_user_tx_valid ;

wire w_user_tx_ready ;

wire [P_USER_DATA_WIDTH - 1 : 0] w_user_rx_data ;

wire w_user_rx_valid ;

wire w_user_active ;

wire w_user_clk ;

wire w_user_rst ;

assign w_user_active = r_user_tx_valid & w_user_tx_ready;uart_drive#(.P_SYSTEM_CLK (50_000_000 ), //输入时钟频率.P_UART_BUADRATE (9600 ), //波特率.P_UART_DATA_WIDTH (P_USER_DATA_WIDTH ), //数据宽度.P_UART_STOP_WIDTH (1 ), //1或者2.P_UART_CHECK (2 ) //None=0 Odd-1 Even-2

)

uart_drive_u0

( .i_clk (clk),.i_rst (rst), .i_uart_rx (o_uart_tx ),.o_uart_tx (o_uart_tx ),.i_user_tx_data (r_user_tx_data ),.i_user_tx_valid (r_user_tx_valid ),.o_user_tx_ready (w_user_tx_ready ),.o_user_rx_data (w_user_rx_data ),.o_user_rx_valid (w_user_rx_valid ),.o_user_clk (w_user_clk ) ,.o_user_rst (w_user_rst )

);/****激励信号****/

always@(posedge w_user_clk,posedge w_user_rst)

beginif(w_user_rst)r_user_tx_data <= 'd0;else if(w_user_active)r_user_tx_data <= r_user_tx_data + 1;else r_user_tx_data <= r_user_tx_data;

endalways@(posedge w_user_clk,posedge w_user_rst)

beginif(w_user_rst)r_user_tx_valid <= 'd0;else if(w_user_active)r_user_tx_valid <= 'd0;else if(w_user_tx_ready)r_user_tx_valid <= 'd1;else r_user_tx_valid <= r_user_tx_valid;

endendmodule二、仿真结果

总结

还得练,要熟练使用modelsim进行仿真,因为比vivado快。

要会写仿真代码文件,继续多练。

结合协议时序实现UART收发器也算完结了。

查看全文

99%的人还看了

相似问题

- vivado产生报告阅读分析15-时序报告11

- vivado产生报告阅读分析12-时序报告8

- 多维时序 | MATLAB实现PSO-BiGRU-Attention粒子群优化双向门控循环单元融合注意力机制的多变量时间序列预测

- FPGA时序约束(七)文献时序约束、LogicLock、Design Partition

- 时序预测 | Python实现ConvLSTM卷积长短期记忆神经网络股票价格预测(Conv1D-LSTM)

- 从一到无穷大 #19 TagTree,倒排索引入手是否是优化时序数据库查询的通用方案?

- FPGA设计时序约束八、others类约束之Set_Case_Analysis

- 时序预测 | MATLAB实现WOA-CNN-BiLSTM-Attention时间序列预测(SE注意力机制)

- 多维时序 | MATLAB实现TCN-selfAttention自注意力机制结合时间卷积神经网络多变量时间序列预测

- 【Excel】如何画不同时序交叉的百分比堆积柱状图

猜你感兴趣

版权申明

本文"FPGA-结合协议时序实现UART收发器(六):仿真模块SIM_uart_drive_TB":http://eshow365.cn/6-10719-0.html 内容来自互联网,请自行判断内容的正确性。如有侵权请联系我们,立即删除!